Understanding DIP: Dual In-line Package Explained

Dual In-line Package (DIP) CPU chips have been key in microelectronics, offering a practical, reliable design that simplifies assembly and ensures versatility. With dual rows of parallel pins, these chips were initial in circuit board design, allowing easy socket insertion or soldering. Over time, DIP packaging has adapted to diverse configurations, materials, and sealing methods for specific needs. This article explores DIP basics, their historical importance, and their ongoing role in modern electronics, covering structure, pin configurations, applications, and derivative packages. Whether prototyping or studying legacy systems, discover the lasting impact of DIP technology.Catalog

Overview

DIP (Dual In-line Package) CPU chips stand out with their distinctive design featuring two parallel rows of pins. This thoughtful engineering allows for smooth insertion into compatible chip sockets or direct mounting onto circuit boards that have matching solder hole configurations. The process of inserting and removing these chips requires careful attention; any mishandling could result in pin damage, which might subsequently lead to functionality issues or even complete chip failure.

The DIP package is not a singular entity; it comprises a range of configurations, such as multilayer ceramic, single-layer ceramic, and lead frame types. Each of these variations brings its own set of characteristics that can significantly affect performance and suitability for various applications. For example, multilayer ceramic packages are often the preferred choice in high-frequency applications, owing to their exceptional electrical performance and thermal stability. Conversely, plastic encapsulation serves as a budget-friendly option for mass production, effectively balancing performance with cost considerations.

In addition, the selection of packaging methods—such as glass ceramic sealing or low melting glass packaging—significantly impacts the chips' longevity and reliability. Glass ceramic sealing, for instance, offers outstanding protection against environmental challenges, thereby enhancing the chip's durability in demanding conditions. This aspect becomes particularly important in industries where chips endure extreme temperatures or moisture, such as automotive or aerospace sectors.

Applications of DIP

DIP (Dual In-line Package) packaging has been an initial element in integrated circuits, encompassing a wide range of components such as DIP switches, LEDs, seven-segment displays, bar graph displays, and relays. Introduced in 1964 by Bryant Buck Rogers of Express Semiconductor with a 14-pin variant, its rectangular design offered a compact and efficient arrangement compared to older round components. DIP connectors also became basic to computer and electronic cabling systems, reinforcing their versatility and widespread use.

The design of DIP packages excels in automated assembly processes, enabling efficient techniques like wave soldering to handle multiple integrated circuits simultaneously, significantly reducing manual labor. Their compatibility with breadboards has made them requisite for prototyping, allowing you to swap components effortlessly during design iterations. This adaptability ensured their popularity in various applications, mostly in the 1970s and 1980s when DIP packages dominated the microelectronics landscape.

However, as the industry evolved, surface-mount packages such as PLCC and SOIC surpassed DIP in mass production efficiency. While these newer formats are less compatible with breadboarding, adapters now enable surface-mount devices (SMDs) to integrate into DIP configurations, bridging modern technology with traditional prototyping needs. Although DIP packages were historically favored for programmable components like EPROMs and GALs due to their compatibility with external programming devices, the shift toward in-system programming (ISP) and compact designs has largely transitioned new programmable components to surface-mount formats, reflecting the industry's focus on miniaturization and efficiency.

Structure of DIP

DIP (Dual In-line Package) chips are primarily encased in either plastic or ceramic materials, each offering unique benefits tailored to various application requirements. Ceramic packages are mostly esteemed for their exceptional airtightness, making them a favored option in high-reliability sectors such as aerospace and medical devices. These environments necessitate remarkable durability and strong resistance to environmental influences, qualities that ceramic materials naturally possess. The longevity and stability of ceramic encasements ensure that the chips retain their functionality over extended durations, even when faced with harsh conditions.

On the other hand, most DIP chips are typically housed in thermosetting resin plastic. This material is appreciated for its rapid processing capabilities, allowing you to produce substantial quantities of chips with remarkable efficiency. The swift production capabilities of thermosetting plastics not only address the rising demand for electronic components but also align with the fast-evolving landscape of high-tech advancements. This manufacturing efficiency plays a substantial role, enabling you to introduce innovations to the market promptly, thus meeting consumer expectations for cutting-edge technology.

In addition, the selection of packaging material has a profound impact on the thermal and electrical performance of the chips. While thermosetting plastics offer advantages for large-scale production, they may lack the thermal conductivity that ceramics provide. This aspect becomes mostly used in applications where effective heat dissipation is a must, such as in high-performance computing or power management systems. Consequently, you can frequently encounter the challenge of balancing production efficiency with performance needs, sparking ongoing discussions about the most suitable materials for specific applications.

Number of Pins and Pitch of DIP

|

Parameter |

Details |

|

Pitch (Pin Spacing) |

- Common: 0.1 inches (2.54 mm) |

|

- Less Common: 0.07 inches (1.778 mm) |

|

|

Row Spacing |

- Common: 0.3 inches (7.62 mm), 0.6 inches (15.24 mm) |

|

- Less Common: 0.4 inches (10.16 mm), 0.9 inches (22.86

mm), 0.75 inches (19.05 mm) |

|

|

Metric Pitch |

- Soviet/Eastern European Standard: 2.5 mm |

|

Number of Pins (0.3” Spacing) |

- Common: 8, 16, 20, 24 |

|

- Rare: 4, 28 |

|

|

Number of Pins (0.6” Spacing) |

- Common: 24, 28, 32, 40 |

|

- Rare: 36, 48, 52 |

|

|

Maximum Number of Pins |

- Motorola 68000 and Zilog Z180 CPUs: 64 pins |

Direction and Pin Number of DIP

When the identification notch of a component is positioned upward, the pin located at the top left is marked as pin 1. The remaining pins are then numbered in a counterclockwise direction. This systematic method plays a notable role in establishing correct connections and ensuring the functionality of integrated circuits (ICs). For example, in a DIP14 IC, pin 1 is situated on the left side at the top, with pins 1 through 7 descending on the left and pins 8 through 14 ascending on the right.

Grasping the orientation of pins is active for effective electronic circuit design and implementation. Misidentifying PINs can lead to incorrect connections, which may cause circuit failure or damage to components. This highlights the necessity for meticulous attention to detail during the assembly process. You can often cultivate a practice of cross-referencing pin configurations with datasheets before soldering components onto a PCB. Such diligence not only reduces the likelihood of errors but also contributes to the overall reliability of the final product.

The pin numbering system serves as a standard that promotes interoperability among various components. Familiarizing oneself with the pinout diagrams provided proves advantageous when designing a circuit. These diagrams act as visual aids, clearly depicting the function of each pin along with its corresponding number. Additionally, maintaining a consistent method for labeling and documenting pin configurations during prototyping can greatly facilitate troubleshooting and future modifications.

Further Derivative Packages

The SOIC (Small Outline IC) package stands out as a widely embraced surface mount technology mostly favored in consumer electronics and personal computers. Its design is a more compact variation of the standard PDIP (Plastic Dual In-line Package), featuring pins arranged on both sides to maximize space efficiency. This thoughtful design resonates with the growing trend towards miniaturization in modern electronics, where compactness is not just a preference but a necessity driven by consumer demands.

In addition to SOIC, other similar packaging methods contribute to the industry landscape. These include:

• SOJ (Small Outline J-lead): Often chosen for memory devices, SOJ packages boast specific pin configurations that enhance both connectivity and performance.

• SOP (Small Outline Package): Known for offering a wider variety of pin counts and sizes, SOP packages provide versatility across numerous applications.

When selecting a package type, a range of design considerations come into play, each with its own implications.

• Thermal performance: The capacity of a package to effectively dissipate heat is dominant; inadequate heat management can jeopardize the reliability of the device.

• Material choice: The selection of materials plays a crucial role in the overall integrity and longevity of the package.

• Pin layout: The arrangement of pins can significantly affect electromagnetic interference (EMI) characteristics, which are dynamic in densely populated circuit boards.

By carefully observing these factors, you can create more resilient packages that not only meet current technical demands but also endure the test of time.

Features of DIP Packages

|

Feature |

Description |

|

Ease of Operation |

Suitable for perforating and soldering on PCB (printed

circuit board), easy to operate. |

|

Chip-to-Package Area Ratio |

The ratio between the chip area and the package area is

large, resulting in a larger volume. |

|

Historical Use in CPUs |

Used in the earliest CPUs like 4004, 8008, 8086, and

8088. The two rows of pins can be inserted into motherboard slots or soldered

directly. |

|

Popularity in Memory Particles |

In the era when memory particles were directly plugged

onto the motherboard, DIP packaging was widely used. |

|

SDIP (Shrink DIP) Derivative |

Offers six times higher pin density compared to

traditional DIP packaging. |

|

DIP as a Switch |

DIP also refers to DIP switches, with specific electrical

characteristics: |

|

-Electrical Life: Tested under 24VDC voltage and

25mA current, lasting up to 2000 toggles. |

|

|

- Rated Current (Not Switched Frequently): 100mA,

withstands 50VDC. |

|

|

- Rated Current (Frequently Switched): 25mA,

withstands 24VDC. |

|

|

- Contact Impedance: (a) Initial value: 50mΩ maximum; (b)

Post-test value: 100mΩ maximum. |

|

|

- Insulation Resistance: Minimum 100mΩ at 500VDC. |

|

|

- Compressive Strength: 500VAC for 1 minute. |

|

|

- Polar Capacitance: Maximum 5pF. |

|

|

- Loop Type: Single contact single selection: DS(S),

DP(L). |

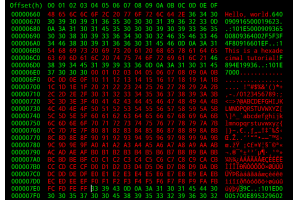

DIP (Digital Image Processor) 2D Image

Utilization of DIP-Packaged Chips

DIP-packaged chips, identifiable by their dual rows of pins, present a flexible solution for incorporation into various electronic systems. These chips can be easily soldered into DIP sockets or directly onto circuit boards. This method of through-hole soldering not only simplifies the assembly process but also resonates with the hands-on nature of learning and experimentation. Such ease of use is mostly advantageous in educational environments and prototyping scenarios, where the ability to quickly iterate designs is highly valued.

Nevertheless, while the design of DIP packages promotes compatibility with motherboards, several challenges warrant consideration. The larger footprint and increased thickness of these packages can create spatial limitations on densely populated circuit boards. Additionally, the exposed pins are susceptible to damage during handling, potentially exposing the reliability of connections. Practical experience indicates that careful handling practices and protective measures, such as using anti-static bags, can help alleviate these concerns.

Typically, DIP packages accommodate a maximum of 100 pins, reflecting a thoughtful balance between functionality and manufacturability. As advancements in CPU integration have progressed, the prevalence of DIP packaging has waned, making way for more compact and efficient packaging technologies. This transition signifies a broader trend in the electronics industry towards miniaturization and enhanced integration, aiming to improve performance while conserving space.

About us

ALLELCO LIMITED

Read more

Quick inquiry

Please send an inquiry, we will respond immediately.

HEX: The Language of Digital Systems

on December 30th

Multipliers in Electronics: Principles, Types, and Applications

on December 30th

Popular Posts

-

Complex Instruction Set Computers: How They Changed Computing?

on April 18th 147749

-

USB-C Pinout and Features

on April 18th 111916

-

Using Xilinx Unified Simulation Primitives: A Comprehensive Guide to FPGA Design and Simulation

on April 18th 111349

-

Power Supply Voltages in Electronics: Meaning of VCC, VDD, VEE, VSS, and GND

on April 18th 83714

-

RJ45 Connector Guide: Pinout, Wiring, Cable Types, and Uses

on January 1th 79502

-

The Ultimate Guide to Wire Color Codes in Modern Electrical Systems

The way our electrical systems use colors isn’t just for looks. Each wire color now indicates a specific function, making it easier to identify and handle electrical components correctly during ins...on January 1th 66871

-

Quality (Q) Factor: Equations and Applications

The quality factor, or 'Q', is important when checking how well inductors and resonators work in electronic systems that use radio frequencies (RF). 'Q' measures how well a circuit minimizes energy...on January 1th 63005

-

Purge Valve Guide: Function, Symptoms, Testing, and Replacement for Optimal Engine Performance

The purge valve is a key part of a car’s system that helps keep the air clean by managing fuel vapors before they can escape into the atmosphere. This not only helps the environment by reducing pol...on January 1th 62948

-

Achieving Peak Performance with the Maximum Power Transfer Theorem

The Maximum Power Transfer Theorem explains how energy from a source, such as a battery or generator, flows to a connected load. It shows the exact condition where the load receives the most power....on January 1th 54077

-

A23 Battery Specifications and Compatibility

The A23 battery is a small, cylinder-shaped battery with high voltage. Also called 23A, 23AE, or MN21, it runs at 12 volts and much higher than AA or AAA batteries. Its special design make...on January 1th 52091