# Triple Half-Bridge Driver with SPI Control

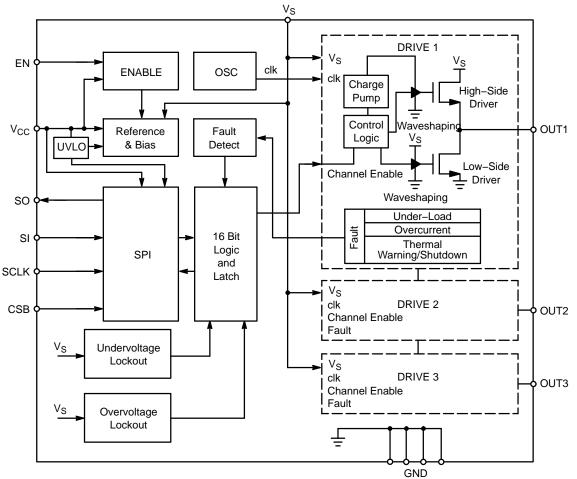

The NCV7703B is a fully protected Triple Half–Bridge Driver designed specifically for automotive and industrial motion control applications. The three half–bridge drivers have independent control. This allows for high side, low side, and H–Bridge control. H–Bridge control provides forward, reverse, brake, and high impedance states. The drivers are controlled via a standard Serial Peripheral Interface (SPI). This device is fully compatible with ON Semiconductor's NCV7708 Double Hex Driver.

# Features

- Ultra Low Quiescent Current in Sleep Mode, 1  $\mu$ A for V<sub>S</sub> and V<sub>CC</sub>

- Power Supply Voltage Operation down to 5 V

- 3 High–Side and 3 Low–Side Drivers Connected as Half–Bridges

- Internal Free–Wheeling Diodes

- Configurable as H–Bridge Drivers

- 0.5 A Continuous (1 A peak) Current

- $R_{DS(on)} = 0.8 \Omega (typ)$

- 5 MHz SPI Control with Daisy Chain Capability

- Compliance with 5 V and 3.3 V Systems

- Overvoltage and Undervoltage Lockout

- Fault Reporting

- 1.4 A Overcurrent Threshold Detection with Optional Shutdown

- 3 A Current Limit with Auto Shutdown

- Overtemperature Warning and Protection Levels

- Internally Fused Leads in SOIC–14 Package for Better Thermal Performance

- ESD Protection up to 6 kV

- These are Pb–Free Devices

# **Typical Applications**

- Automotive

- Industrial

- DC Motor Management

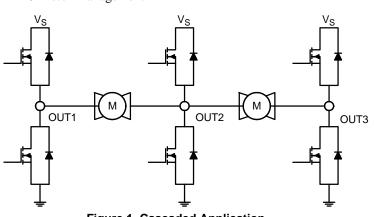

Figure 1. Cascaded Application

# **ON Semiconductor®**

www.onsemi.com

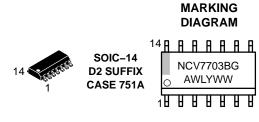

NCV7703B = Specific Device Code

A = Assembly Location

WL = Wafer Lot Y = Year

Y = Year WW = Work Week

G = Pb-Free Package

#### **PIN CONNECTIONS**

| GND 📼            | 0 | ╘  | GND             |

|------------------|---|----|-----------------|

| OUT3 📼           |   |    | OUT1            |

| V <sub>S</sub> 📼 |   | ┢╍ | OUT2            |

| CSB 📼            |   | ╘  | V <sub>CC</sub> |

| SI 📼             |   | ╘╍ | EN              |

| SCLK 📼           |   |    | SO              |

| GND 📼            |   | ┢╍ | GND             |

|                  |   |    |                 |

## **ORDERING INFORMATION**

| Device        | Package              | Shipping†             |

|---------------|----------------------|-----------------------|

| NCV7703BD2G   | SOIC-14<br>(Pb-Free) | 55 Units / Rail       |

| NCV7703BD2R2G | SOIC-14<br>(Pb-Free) | 2500 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

Figure 2. Block Diagram

#### PACKAGE PIN DESCRIPTION

| Pin # | Symbol          | Description                                                            |  |  |  |

|-------|-----------------|------------------------------------------------------------------------|--|--|--|

| 1     | GND*            | Ground. Connect all grounds together.                                  |  |  |  |

| 2     | OUT3            | Half Bridge Output 3.                                                  |  |  |  |

| 3     | VS              | Power Supply input for the output drivers and internal supply voltage. |  |  |  |

| 4     | CSB             | Chip Select Bar. Active low serial port operation.                     |  |  |  |

| 5     | SI              | Serial Input                                                           |  |  |  |

| 6     | SCLK            | Serial Clock                                                           |  |  |  |

| 7     | GND*            | Ground. Connect all grounds together.                                  |  |  |  |

| 8     | GND*            | Ground. Connect all grounds together.                                  |  |  |  |

| 9     | SO              | Serial Output                                                          |  |  |  |

| 10    | EN              | Enable. Logic high wakes the IC up from a sleep mode.                  |  |  |  |

| 11    | V <sub>CC</sub> | Power supply input for internal logic.                                 |  |  |  |

| 12    | OUT2            | Half Bridge Output 2.                                                  |  |  |  |

| 13    | OUT1            | Half Bridge Output 1.                                                  |  |  |  |

| 14    | GND*            | Ground. Connect all grounds together.                                  |  |  |  |

\*Pins 1, 7, 8, and 14 are internally shorted together. It is recommended to also short these pins externally.

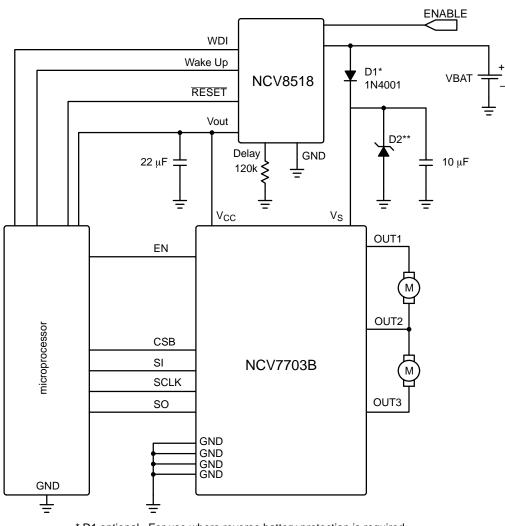

\* D1 optional. For use where reverse battery protection is required. \*\* D2 optional. For use where load dump exceeds 40V.

Figure 3. Application Circuit

# **MAXIMUM RATINGS**

| Rating                                                                                   | Value                             | Unit |

|------------------------------------------------------------------------------------------|-----------------------------------|------|

| Power Supply Voltage (V <sub>S</sub> )<br>(DC)<br>(AC), t < 500 ms, lvs > $-2$ A         | -0.3 to 40<br>-1                  | V    |

| Output Pin OUTx<br>(DC)<br>(AC), t < 500 ms, IOUTx > $-2$ A                              | -0.3 to 40<br>-1                  | V    |

| Pin Voltage<br>(Logic Input pins, SI, SCLK, CSB, SO, EN, V <sub>CC</sub> )               | -0.3 to 7                         | V    |

| Output Current (OUTx)<br>(DC)<br>(AC) (50 ms pulse, 1 s period)                          | -1.8 to 1.8<br>Internally Limited | A    |

| Electrostatic Discharge, Human Body Model,<br>V <sub>S</sub> , OUT1, OUT2, OUT3 (Note 3) | 6                                 | kV   |

| Electrostatic Discharge, Human Body Model,<br>all other pins (Note 3)                    | 2                                 | kV   |

| Electrostatic Discharge, Machine Model,<br>V <sub>S</sub> , OUT1, OUT2, OUT3 (Note 3)    | 300                               | V    |

| Electrostatic Discharge, Machine Model,<br>all other pins (Note 3)                       | 200                               | V    |

| Operating Junction Temperature                                                           | -40 to 150                        | °C   |

| Storage Temperature Range                                                                | -55 to 150                        | °C   |

| Moisture Sensitivity Level (MAX 260°C Processing)                                        | MSL3                              | -    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

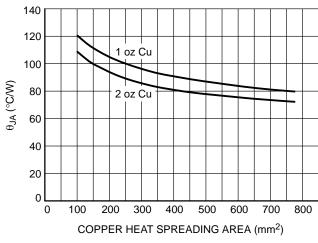

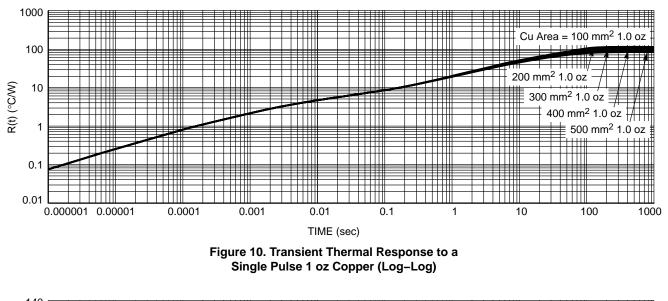

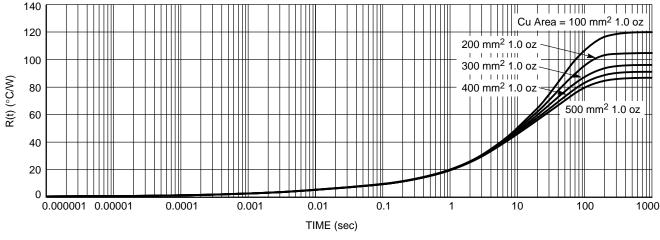

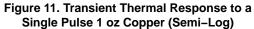

| Thermal Parameters                                                   | Test Conditions           | Unit                     |      |

|----------------------------------------------------------------------|---------------------------|--------------------------|------|

| 14 Pin Fused SOIC Package                                            | min–pad board<br>(Note 1) | 1″ pad board<br>(Note 2) |      |

| Junction–to–Lead (psi–JL8, $\Psi_{\text{JL8}}$ ) or Pins 1, 7, 8, 14 | 23                        | 22                       | °C/W |

| Junction–to–Ambient ( $R_{\theta JA}, \theta_{JA}$ )                 | 122                       | 83                       | °C/W |

1. 1-oz copper, 67 mm<sup>2</sup> copper area, 0.062" thick FR4.

2. 1-oz copper, 645 mm<sup>2</sup> copper area, 0.062" thick FR4.

3. This device series incorporates ESD protection and is characterized by the following methods: ESD HBM according to AEC-Q100-002 (EIA/JESD22-A114) ESD MM according to AEC-Q100-003 (EIA/JESD22-A115)

# **ELECTRICAL CHARACTERISTICS**

(-40°C  $\leq$  TJ  $\leq$  150°C, 5.5 V  $\leq$  VS  $\leq$  40 V, 3 V  $\leq$  VCC  $\leq$  5.25 V, EN = VCC, unless otherwise specified)

| Characteristic                                                 |                         | Conditions                                                                                                                                                                                                                | Min         | Тур         | Max         | Unit    |

|----------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|---------|

| GENERAL                                                        |                         |                                                                                                                                                                                                                           |             |             |             |         |

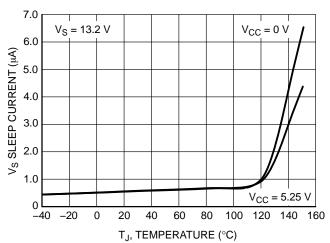

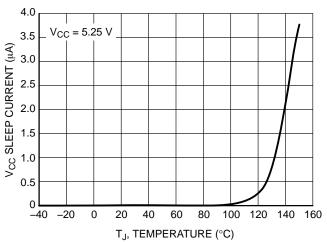

| Supply Current (V <sub>S</sub> )<br>Sleep Mode (Note 5)        |                         | $\begin{split} V_{S} &= 13.2 \text{ V, OUTx} = 0 \text{ V} \\ EN &= SI = SCLK = 0 \text{ V, CSB} = V_{CC} \\ 0 \text{ V} &< V_{CC} < 5.25 \text{ V} \\ (T_{J} &= -40^{\circ}\text{C to } 85^{\circ}\text{C}) \end{split}$ | -           | 1.0         | 5.0         | μΑ      |

|                                                                |                         | $V_{S} = 13.2 V$ , OUTx = 0 V<br>EN = SI = SCLK = 0 V, CSB = V <sub>CC</sub><br>0 V < V <sub>CC</sub> < 5.25 V, T <sub>J</sub> = 25°C                                                                                     | _           | -           | 2.0         |         |

| Supply Current (V <sub>S</sub> )<br>Active Mode                |                         | EN = V <sub>CC</sub> , 5.5 V < V <sub>S</sub> < 35 V<br>No Load                                                                                                                                                           | -           | 2.0         | 4.0         | mA      |

| Supply Current (V <sub>CC</sub> )<br>Sleep Mode (Note 6)       |                         | $V_{CC} = CSB$ , EN = SI = SCLK = 0 V<br>(T <sub>J</sub> = -40°C to 85°C)                                                                                                                                                 | -           | 0           | 2.5         | μΑ      |

| Supply Current (V <sub>CC</sub> )<br>Active Mode               |                         | EN = V <sub>CC</sub>                                                                                                                                                                                                      | -           | 1.5         | 3.0         | mA      |

| V <sub>CC</sub> Power–On–Reset Threshol                        | d                       |                                                                                                                                                                                                                           | 2.60        | 2.80        | 3.00        | V       |

| V <sub>S</sub> Undervoltage Detection                          | Threshold<br>Hysteresis | V <sub>S</sub> decreasing                                                                                                                                                                                                 | 4.3<br>100  | 4.7<br>-    | 5.1<br>400  | V<br>mV |

| $V_{S}$ Overvoltage Detection                                  | Threshold<br>Hysteresis | V <sub>S</sub> increasing                                                                                                                                                                                                 | 34.0<br>1.5 | 37.5<br>3.5 | 40.0<br>5.5 | V       |

| Thermal Warning (Note 4)                                       | Threshold<br>Hysteresis |                                                                                                                                                                                                                           | 120<br>-    | 145<br>30   | 170<br>-    | °C      |

| Thermal Shutdown (Note 4)                                      | Threshold<br>Hysteresis |                                                                                                                                                                                                                           | 155<br>-    | 175<br>30   | 195<br>-    | °C      |

| Ratio of Thermal Shutdown to T<br>Warning temperature (Note 4) | hermal                  |                                                                                                                                                                                                                           | 1.05        | 1.20        | -           | °C/°C   |

# OUTPUTS

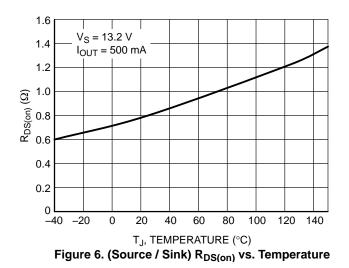

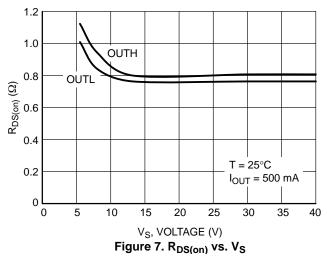

| Output R <sub>DS(on)</sub> (Source) | $I_{out} = -500 \text{ mA}$                                                          |   |     |      |   |

|-------------------------------------|--------------------------------------------------------------------------------------|---|-----|------|---|

|                                     | $V_{S} = 13.2 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$                         | - | 0.8 | 0.95 | Ω |

|                                     | V <sub>S</sub> = 13.2 V                                                              | - | -   | 1.5  | Ω |

|                                     | $8 \text{ V} \le \text{V}_{\text{S}} \le 40 \text{ V}$                               | - | -   | 1.7  | Ω |

|                                     | $5.5 \text{ V} \le \text{V}_{S} \le 8 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$ | - | 1.3 | -    | Ω |

|                                     | $5.5 \text{ V} \le \text{V}_S \le 8 \text{ V}$                                       | - | -   | 2.0  | Ω |

| Output R <sub>DS(on)</sub> (Sink)   | I <sub>out</sub> = 500 mA                                                            |   |     |      |   |

|                                     | $V_{S} = 13.2 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$                         | - | 0.8 | 0.95 | Ω |

|                                     | V <sub>S</sub> = 13.2 V                                                              | - | -   | 1.5  | Ω |

|                                     | $8 \text{ V} \le \text{V}_{\text{S}} \le 40 \text{ V}$                               | - | -   | 1.7  | Ω |

|                                     | 5.5 V $\leq$ V_S $\leq$ 8 V, T_J = 25°C                                              | - | 1.3 | -    | Ω |

|                                     | $5.5 \text{ V} \le \text{V}_{\text{S}} \le 8 \text{ V}$                              | - | -   | 2.0  | Ω |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Thermal characteristics are not subject to production test

5. For temperatures above 85°C, refer to Figure 4.

6. For temperatures above 85°C, refer to Figure 5.

# **ELECTRICAL CHARACTERISTICS**

(-40°C  $\leq$  T\_J  $\leq$  150°C, 5.5 V  $\leq$  V\_S  $\leq$  40 V, 3 V  $\leq$  V\_{CC}  $\leq$  5.25 V, EN = V\_{CC}, unless otherwise specified)

| Characteristic                                       |                | Conditions                                                                                                                                                                                                                              | Min         | Тур         | Max         | Unit |

|------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|------|

| OUTPUTS                                              |                |                                                                                                                                                                                                                                         |             |             |             |      |

| Source Leakage Current<br>Sum of I(OUTx) x = 1, 2, 3 |                | $\begin{array}{l} {\rm OUTx} = 0 \ {\rm V}, \ {\rm V}_{\rm S} = 40 \ {\rm V}, \ {\rm EN} = 0 \ {\rm V} \\ {\rm CSB} = {\rm V}_{\rm CC} \\ 0 \ {\rm V} < {\rm V}_{\rm CC} < 5.25 \ {\rm V} \\ {\rm Sum}({\rm I}({\rm OUTx}) \end{array}$ | -5.0        | _           | -           | μΑ   |

|                                                      |                | OUTx = 0 V, $V_S$ = 40 V, EN = 0 V<br>CSB = V <sub>CC</sub><br>0 V < V <sub>CC</sub> < 5.25 V, T <sub>J</sub> = 25°C<br>Sum(I(OUTx)                                                                                                     | -1.0        | -           | _           |      |

| Sink Leakage Current                                 |                | OUTx = $V_S$ = 40 V, EN = 0 V<br>CSB = $V_{CC}$<br>0 V < $V_{CC}$ < 5.25 V                                                                                                                                                              | _           | -           | 300         | μΑ   |

|                                                      |                | OUTx = $V_S$ = 13.2 V, EN = 0 V<br>CSB = $V_{CC}$<br>0 V < $V_{CC}$ < 5.25 V, T <sub>J</sub> = 25°C                                                                                                                                     | _           | -           | 10          |      |

| Over Current Shutdown Threshold                      | Source<br>Sink |                                                                                                                                                                                                                                         | –1.8<br>1.0 | -1.4<br>1.4 | -1.0<br>1.8 | A    |

| Current Limit                                        | Source<br>Sink |                                                                                                                                                                                                                                         | -5.0<br>2.0 | -3.0<br>3.0 | -2.0<br>5.0 | A    |

| Under Load Detection Threshold                       | Source<br>Sink |                                                                                                                                                                                                                                         | -15<br>3.0  | -7.0<br>7.0 | -2.0<br>15  | mA   |

| Power Transistor Body Diode Forwar                   | d Voltage      | l <sub>f</sub> = 500 mA                                                                                                                                                                                                                 | -           | 0.9         | 1.3         | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Thermal characteristics are not subject to production test

For temperatures above 85°C, refer to Figure 4.

For temperatures above 85°C, refer to Figure 5.

# **ELECTRICAL CHARACTERISTICS**

(-40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C, 5.5 V  $\leq$  V<sub>S</sub>  $\leq$  40 V, 3 V  $\leq$  V<sub>CC</sub>  $\leq$  5.25 V, EN = V<sub>CC</sub>, unless otherwise specified)

| Characteristic                        | Conditions                                        | Min                   | Тур                   | Max     | Unit             |

|---------------------------------------|---------------------------------------------------|-----------------------|-----------------------|---------|------------------|

| LOGIC INPUTS (EN, SI, SCLK, CSB)      | •                                                 | •                     |                       |         |                  |

| Input Threshold                       |                                                   |                       |                       |         | %V <sub>CC</sub> |

| High<br>Low                           |                                                   | -<br>30               | _                     | 70<br>- |                  |

| Input Hysteresis                      |                                                   | 100                   | 350                   | 600     | mV               |

| Input Pulldown Current (EN, SI, SCLK) | $EN = SI = SCLK = V_{CC}$                         | 5.0                   | 25                    | 50      | μΑ               |

| Input Pullup Current (CSB)            | CSB = 0 V                                         | -50                   | -25                   | -5      | μA               |

| Input Capacitance (Note 7)            |                                                   | -                     | 10                    | 15      | pF               |

| LOGIC OUTPUT (SO)                     | -                                                 |                       |                       |         | -                |

| Output High                           | I <sub>out</sub> = 1 mA                           | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> – 0.7 | -       | V                |

| Output Low                            | $I_{out} = -1.6 \text{ mA}$                       | -                     | 0.2                   | 0.4     | V                |

| Tri-state Leakage                     | $CSB = V_{CC}, 0 V \le SO \le V_{CC}$             | -10                   | -                     | 10      | μΑ               |

| Tri-state Input Capacitance (Note 7)  | $CSB = V_{CC}$                                    | -                     | 10                    | 15      | pF               |

| TIMING SPECIFICATIONS                 |                                                   |                       |                       |         |                  |

| Overcurrent Shutdown Delay Time       |                                                   |                       |                       |         | μs               |

| Source                                |                                                   | 10                    | 25                    | 50      |                  |

| Sink                                  |                                                   | 10                    | 25                    | 50      |                  |

| Current Limit Fault Delay             | V <sub>S</sub> > 8 V                              | -                     | 200                   | -       | μS               |

| Under Load Detection Delay Time       |                                                   | 200                   | 350                   | 600     | μs               |

| High Side Turn On Time                | $V_{S}$ = 13.2 V, R <sub>load</sub> = 25 $\Omega$ | -                     | 7.5                   | 15      | μs               |

| High Side Turn Off Time               | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 3.0                   | 6.0     | μs               |

| Low Side Turn On Time                 | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 6.5                   | 15      | μs               |

| Low Side Turn Off Time                | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 3.0                   | 6.0     | μs               |

| High Side Rise Time                   | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 5.0                   | 10      | μs               |

| High Side Fall Time                   | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 2.0                   | 5.0     | μs               |

| Low Side Rise Time                    | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 1.0                   | 3.0     | μs               |

| Low Side Fall Time                    | $V_{S}$ = 13.2 V, $R_{load}$ = 25 $\Omega$        | -                     | 1.0                   | 3.0     | μs               |

| NonOverlap Time                       | High Side Turn Off to Low Side Turn On            | 1.0                   | _                     | -       | μs               |

| NonOverlap Time                       | Low Side Turn Off to High Side Turn On            | 1.0                   | -                     | -       | μs               |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 7. Not production tested.

# **ELECTRICAL CHARACTERISTICS**

(-40°C  $\leq$  T\_J  $\leq$  150°C, 5.5 V  $\leq$  V\_S  $\leq$  40 V, 3 V  $\leq$  V\_{CC}  $\leq$  5.25 V, EN = V\_{CC}, unless otherwise specified)

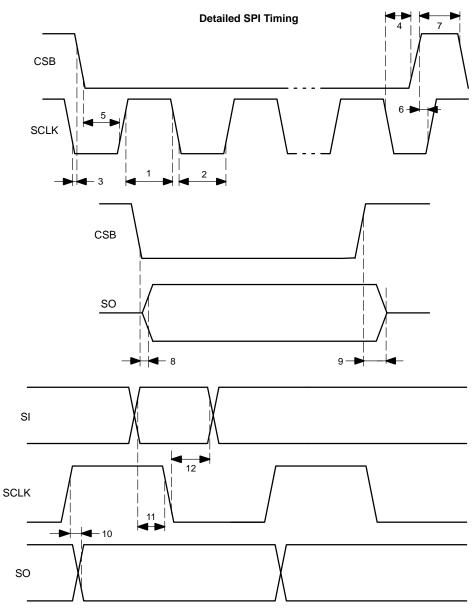

# SERIAL PERIPHERAL INTERFACE

| Characteristic                            | Conditions                                               | Timing Chart #<br>(See Figure 8) | Min        | Тур | Max | Unit |

|-------------------------------------------|----------------------------------------------------------|----------------------------------|------------|-----|-----|------|

| SCLK Frequency                            | V <sub>CC</sub> = 5 V                                    | -                                | -          | -   | 5   | MHz  |

| SCLK Clock Period                         | V <sub>CC</sub> = 5 V<br>V <sub>CC</sub> = 3.3 V         |                                  | 200<br>500 |     |     | ns   |

| Maximum Input Capacitance (Note 8)        | SI, SCLK                                                 | _                                | -          | -   | 15  | pF   |

| SCLK High Time                            |                                                          | 1                                | 85         | -   | -   | ns   |

| SCLK Low Time                             |                                                          | 2                                | 85         | -   | -   | ns   |

| SCLK Setup Time                           |                                                          | 3<br>4                           | 85<br>85   |     |     | ns   |

| SI Setup Time                             |                                                          | 11                               | 50         | -   | -   | ns   |

| SI Hold Time                              |                                                          | 12                               | 50         | -   | -   | ns   |

| CSB Setup Time                            |                                                          | 5<br>6                           | 100<br>100 |     | -   | ns   |

| CSB High Time (Note 9)                    |                                                          | 7                                | 200        | -   | -   | ns   |

| SO enable after CSB falling edge (Note 8) |                                                          | 8                                | -          | -   | 50  | ns   |

| SO disable after CSB rising edge (Note 8) |                                                          | 9                                | -          | -   | 50  | ns   |

| SO Rise Time                              | $V_{CC}$ = 5 V, $C_{load}$ = 40 pF                       | -                                | _          | 10  | 25  | ns   |

| SO Fall Time                              | $V_{CC} = 5 \text{ V}, \text{ C}_{load} = 40 \text{ pF}$ | -                                | -          | 10  | 25  | ns   |

| SO Valid Time (Note 8)                    | SCLK ↑ to SO 50%                                         | 10                               | -          | 20  | 50  | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 8. Not tested in production.

9. Minimum high time of CSB between two successive SPI commands.

# **TYPICAL CHARACTERISTICS**

Figure 4. V<sub>S</sub> Sleep Supply Current vs. Temperature

Figure 5. V<sub>CC</sub> Sleep Supply Current vs. Temperature

# **TYPICAL CHARACTERISTICS**

Figure 9.  $\theta_{JA}$  vs. Copper Spreader Area, 14 Lead SON (fused leads)

# **SPI** Communication

Standard 16-bit communication has been implemented to this IC to turn drivers on/off, and to report faults. (See Figure 13). The LSB (Least Significant Bit) is clocked in first.

# Communication is Implemented as Follows:

- 1. CSB goes low to allow serial data transfer.

- 2. A 16 bit word is clocked (SCLK) into the SI (Serial Input) pin.

- 3. CSB goes high to transfer the clocked in information to the data registers.

- NOTE: SO is tristate when CSB is high.

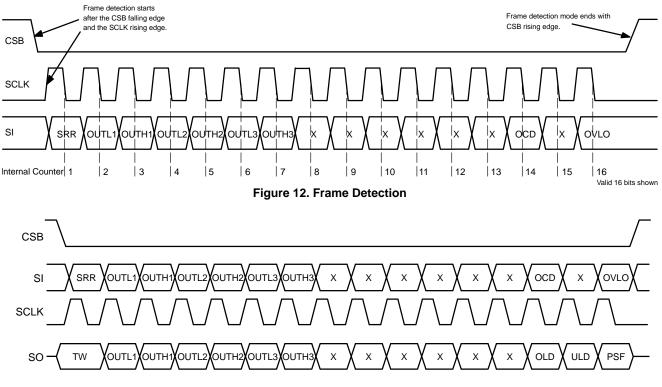

# **Frame Detection**

Input word integrity (SI) is evaluated by the use of a frame consistency check. The word frame length is compared to an  $\eta \ge 16$  bit acceptable word length before the data is latched into the input register. This guarantees the proper word length has been imported and allows for daisy chain operation applications.

The frame length detector is enabled with the CSB falling edge and the SCLK rising edge.

SCLK must be low during the CSB rising edge. The fault register is cleared with a valid frame detection. Existing faults are re–latched after the fault filter time.

Figure 13. SPI Communication Frame Format

Table 1 defines the programming bits and diagnostic bits. Figure 13 displays the timing diagram associated with Table 1. Fault information is sequentially clocked out the SO pin of the NCV7703B as programming information is clocked into the SI pin of the device. Daisy chain communication between SPI compatible IC's is possible by connection of the Serial Output pin (SO) to the input of the sequential IC (SI) (Reference the Daisy Chain Section).

# Table 1. SPI BIT DESCRIPTION

|            | Input Data                  |              |            | Output Data                    |               |

|------------|-----------------------------|--------------|------------|--------------------------------|---------------|

| Bit Number | Bit Description             | Bit Status   | Bit Number | Bit Description                | Bit Status    |

| 15         | Over Voltage Lock Out       | 0 = Disable  | 15         | Power Supply Fail Signal       | 0 = No Fault  |

|            | Control (OVLO)              | 1 = Enable   |            | (PSF for OVLO or UVLO)         | 1 = Fault     |

| 14         | Not Used                    |              | 14         | Under Load Detect Signal (ULD) | 0 = No Fault  |

|            |                             |              |            |                                | 1 = Fault     |

| 13         | Over Current Detection Shut | 0 = Disable  | 13         | Over Load Detect Signal (OLD)  | 0 = No Fault  |

|            | Down Control (OCD)          | 1 = Enable   |            |                                | 1 = Fault     |

| 12         | Not Used                    |              | 12         | Not Used                       |               |

| 11         | Not Used                    |              | 11         | Not Used                       |               |

| 10         | Not Used                    |              | 10         | Not Used                       |               |

| 9          | Not Used                    |              | 9          | Not Used                       |               |

| 8          | Not Used                    |              | 8          | Not Used                       |               |

| 7          | Not Used                    |              | 7          | Not Used                       |               |

| 6          | OUTH3                       | 0 = Off      | 6          | OUTH3                          | 0 = Off       |

|            |                             | 1 = On       |            |                                | 1 = On        |

| 5          | OUTL3                       | 0 = Off      | 5          | OUTL3                          | 0 = Off       |

|            |                             | 1 = On       |            |                                | 1 = On        |

| 4          | OUTH2                       | 0 = Off      | 4          | OUTH2                          | 0 = Off       |

|            |                             | 1 = On       |            |                                | 1 = On        |

| 3          | OUTL2                       | 0 = Off      | 3          | OUTL2                          | 0 = Off       |

|            |                             | 1 = On       |            |                                | 1 = On        |

| 2          | OUTH1                       | 0 = Off      | 2          | OUTH1                          | 0 = Off       |

|            |                             | 1 = On       |            |                                | 1 = On        |

| 1          | OUTL1                       | 0 = Off      | 1          | OUTL1                          | 0 = Off       |

|            |                             | 1 = On       | ]          |                                | 1 = On        |

| 0          | Status Register Reset (SRR) | 0 = No Reset | 0          | Thermal Warning (TW)           | 0 = Not in TW |

|            |                             | 1 = Reset    |            |                                | 1 = In TW     |

# DETAILED OPERATING DESCRIPTION

#### General

The NCV7703B Triple Half Bridge Driver provides drive capability for 3 Half–Bridge configurations. Each output drive is characterized for a 500 mA load and has a typical 1.4 A surge capability. Strict adherence to integrated circuit die temperature is necessary, with a maximum die temperature of 150°C. This may limit the number of drivers enabled at one time. Output drive control and fault reporting are handled via the SPI (Serial Peripheral Interface) port.

An Enable function (EN) provides a low quiescent sleep current mode when the device is not being utilized. A pull down is provided on the EN, SI and SCLK inputs to ensure they default to a low state in the event of a severed input signal. A pull–up is provided on the CSB input disabling SPI communication in the event of an open CSB input.

# **Power Up/Down Control**

A feature incorporated in the IC is an under voltage lockout circuit that prevents the output drivers from turning on unintentionally.  $V_{CC}$  and  $V_S$  are monitored for undervoltage conditions supporting a smooth turn-on transition. All drivers are initialized in the off (high impedance) condition, and will remain off during a  $V_{CC}$  or  $V_S$  undervoltage condition. This allows power up sequencing of  $V_{CC}$ , and  $V_S$  up to the user. Once  $V_{CC}$  is out of UVLO, SPI communication can begin regardless of the voltage on  $V_S$ . However, drivers will remain off if  $V_S$  is in an undervoltage condition. Hysteresis in the UVLO circuits results in glitch free operation during power up/down.

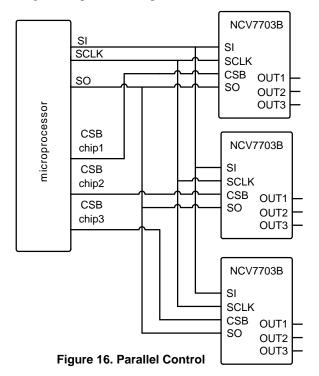

# H–Bridge Driver Configuration

The NCV7703B has the flexibility of controlling each half bridge driver independently. This allows for high side, low side and H–bridge control. H–bridge control provides forward, reverse, brake and high impedance states.

# **Overvoltage Clamping – Driving Inductive Loads**

Each output is internally clamped to ground and Vs by internal free wheeling diodes. The diodes have ratings that complement the FETs they protect.

# **Overcurrent Shutdown Threshold Detection (Table 2)**

The state of input bit 13 (OCD) selects driver reaction when reaching overcurrent shutdown threshold. With a "0" for input bit 13, the OLD status bit will be set to "1" when the level exceeds the overcurrent shutdown shut–down threshold and the driver will remain on. With a "1" for input bit 13, the output driver shuts off when the overcurrent shutdown threshold is exceeded and can only be turned back on via the SPI port with a SPI command that includes an SRR = 1. Note: high currents could cause a high rise in die temperature. Devices will not be allowed to turn on if the die temperature exceeds the thermal shutdown temperature.

# Current Limit Fault

The current limit fault circuit will shut down the offending output driver when the Current Limit (Source or Sink) has

been exceeded for a duration greater than 200  $\mu$ s, regardless of the OLD input bit status. The OUTx output bit will report a "0" indicating which driver encountered the hard short. The OLD status bit will be set and will remain set until a new SRR input SPI command is executed.

# **Under-Load Detection (Table 3)**

The under-load detection circuit monitors the current from each output driver. A minimum load current (this is the maximum open circuit detection threshold) is required when the drivers are turned on. If the under-load detection threshold has been detected for more than the under-load delay time, the ULD bit (output bit #14) will be set to a "1". The under load bit is reset with SRR.

# **Overvoltage Shutdown (Table 4)**

Overvoltage lockout circuitry monitors the voltage on the  $V_S$  pin. The response to an overvoltage condition is selected by SPI input bit 15. PSF output bit 15 is set when a  $V_S$  overvoltage condition exists. If input bit 15 (OVLO) is set to "1", all outputs will turn off during this overvoltage condition. Turn On/Off status is maintained in the logic circuitry, so that when proper input voltage level is reestablished, the programmed outputs will turn back on. The PSF output bit is reset with SRR.

| OLD Input<br>Bit 13 Set | Typical Load Current<br>Condition     | Output Bit 13 OLD Status | OUTx Status                          |

|-------------------------|---------------------------------------|--------------------------|--------------------------------------|

| 0                       | I <sub>L</sub> ≤ 1.4 A                | 0                        | Unchanged                            |

| 0                       | 1.4 A < I <sub>L</sub> $\leq$ 3 A     | 1 (Need SRR to reset)    | Unchanged                            |

| 0                       | $I_L \geq 3$ A, for 200 $\mu s$ (typ) | 1 (Need SRR to reset)    | OUTx Latched Off (Need SRR to reset) |

| 1                       | $I_L \le 1.4 \text{ A}$               | 0                        | Unchanged                            |

| 1                       | $I_L$ > 1.4 A, for 25 $\mu$ s (typ)   | 1 (Need SRR to reset)    | OUTx Latched Off (Need SRR to reset) |

#### Table 2. INPUT BIT 13, OVERCURRENT DETECTION SHUT DOWN CONTROL AND RESPONSE

# Table 3. OUTPUT BIT 14, UNDER LOAD DETECTION SHUT DOWN

| OUTx ULD Set | Output Data Bit 14, Under Load Detect (ULD) Status | OUTx Status |  |

|--------------|----------------------------------------------------|-------------|--|

| 0            | 0                                                  | Unchanged   |  |

| 1            | 1 (Need SRR to reset)                              | Unchanged   |  |

#### Table 4. INPUT BIT 15, OVERVOLTAGE LOCK OUT (OVLO) SHUT DOWN

| OVLO Input<br>Bit 15 | V <sub>S</sub> OVLO<br>Condition | Output Data Bit 15 Power<br>Supply Fail (PSF) Status | OUTx Status                                                  |

|----------------------|----------------------------------|------------------------------------------------------|--------------------------------------------------------------|

| 0                    | 0                                | 0                                                    | Unchanged                                                    |

| 0                    | 1                                | 1 (Need SRR to reset)                                | Unchanged                                                    |

| 1                    | 0                                | 0                                                    | Unchanged                                                    |

| 1                    | 1                                | 1 (Need SRR to reset)                                | All Outputs Shut Off (Remain off until $V_S$ is out of OVLO) |

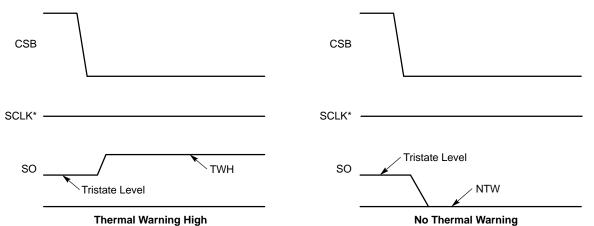

# Thermal Shutdown

Three independent thermal shutdown circuits are featured (one common sensor for each HS and LS transistor pair). Each sensor has two temperature levels; Level 1, Thermal Warning sets the "TW" status bit to a 1 and would have to be reset with a command that includes the SRR after the IC cools to a temperature below Level 1. The output will remain on in this condition.

If the IC temperature reaches Level 2, Over Temperature Shutdown, all drivers are latched off. It can be reset only after the part cools below the shutdown temperature, (including thermal hysteresis) with a turn–on command that includes the SRR set bit.

The output data bit 0, Thermal Warning, will latch and remain set, even after cooling, and is reset by sending a SPI command to reset the status register (SRR, input 0 set to "1"). Since thermal warning precedes a thermal shutdown, software polling of this bit will allow for load control and possible prevention of thermal shutdown conditions.

Thermal warning information can be retrieved immediately without performing a complete SPI access cycle. Figure 14 below displays how this is accomplished. Bringing the CSB pin from a high to low condition immediately displays the information on the Output Data Bit 0, thermal warning, even in the absence of an SCLK signal. As the temperature of the NCV7703B changes from a condition from below the thermal warning threshold to above the thermal warning threshold, the state of the SO pin changes and this level is available immediately when the CSB goes low. A low on SO indicates there is no thermal warning, while a high indicates the IC is above the thermal warning threshold. This warning bit is reset by setting SRR to "1".

\*SCLK can be high or low in order to maintain the thermal information on SO. Toggling SCLK will cause other output bits to shift out. TWH = Thermal Warning High

NTW = No Thermal Warning

# **Applications Drawing**

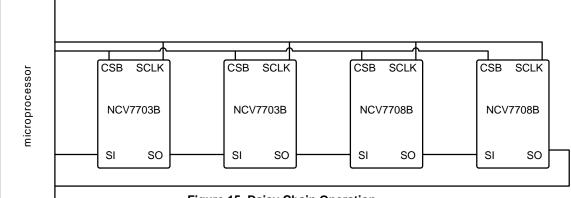

# **Daisy Chain**

The NCV7703B is capable of being setup in a daisy chain configuration with other similar devices which include additional NCV7703B devices as well as the NCV7708 Double Hex Driver. Particular attention should be focused on the fact that the first 16 bits which are clocked out of the SO pin when the CSB pin transitions from a high to a low will be the Diagnostic Output Data. These are the bits representing the status of the IC and are detailed in the SPI Bit Description Table. Additional programming bits should be clocked in which follow the Diagnostic Output bits. Word length must be  $\eta \ge 16$  due to the use of frame detection.

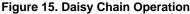

# **Parallel Control**

A more efficient way to control multiple SPI compatible devices is to connect them in a parallel fashion and allow each device to be controlled in a multiplex mode. The diagram below shows a typical connection between the microprocessor or microcontroller and multiple SPI compatible devices. In a daisy chain configuration, the programming information for the last device in the serial string must first pass through all the previous devices. The parallel control setup eliminates that requirement, but at the cost of additional control pins from the microprocessor for each individual CSB pin for each controllable device. Serial data is only recognized by the device that is activated through its respective CSB pin.

#### **Additional Application Setup**

In addition to the cascaded H–Bridge application shown in Figure 1, the NCV7703B can also be used as a high–side driver or low–side driver (Figure 17).

Figure 17. High–Side / Low–Side Application Drawing

Any combination of H-bridge and high or low-side drivers can be designed in. This allows for flexibility in many systems.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **STYLES ON PAGE 2**

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SOIC-14 NB  |                                                                                                                                                                                     | PAGE 1 OF 2 |  |

| ON Semiconductor and () are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the |             |                                                                                                                                                                                     |             |  |

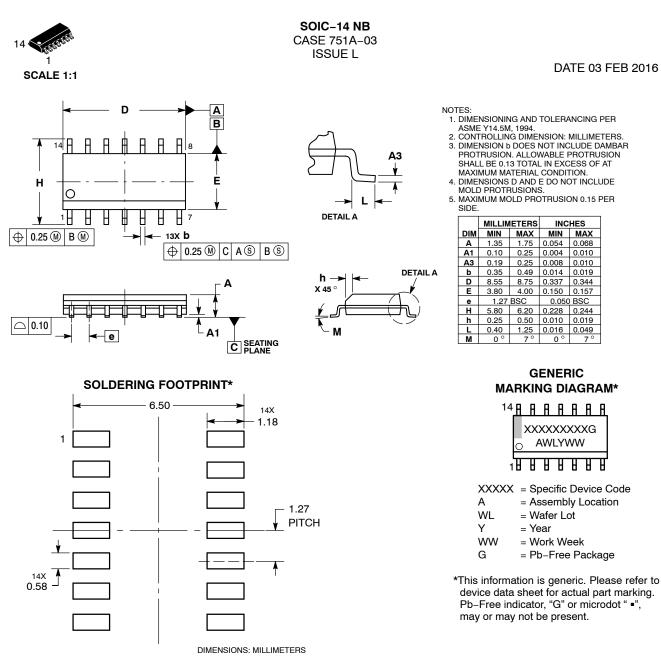

#### SOIC-14 CASE 751A-03 ISSUE L

# DATE 03 FEB 2016

| STYLE 1:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. NO CONNECTION<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                                                                   | STYLE 3:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. ANODE<br>4. NO CONNECTION<br>5. ANODE<br>6. NO CONNECTION<br>7. ANODE<br>8. ANODE<br>9. ANODE<br>10. NO CONNECTION<br>11. ANODE<br>12. ANODE<br>13. NO CONNECTION<br>14. COMMON CATHODE                                            | STYLE 4:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. CATHODE<br>4. NO CONNECTION<br>5. CATHODE<br>6. NO CONNECTION<br>7. CATHODE<br>8. CATHODE<br>10. NO CONNECTION<br>11. CATHODE<br>12. CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. COMMON ANODE<br>8. COMMON CATHODE<br>10. ANODE/CATHODE<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                     | STYLE 6:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE<br>7. CATHODE<br>8. ANODE<br>9. ANODE<br>10. ANODE<br>11. ANODE<br>12. ANODE<br>13. ANODE<br>14. ANODE | STYLE 7:<br>PIN 1. ANODE/CATHODE<br>2. COMMON ANODE<br>3. COMMON CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. COMMON CATHODE<br>12. COMMON ANODE<br>13. ANODE/CATHODE<br>14. ANODE/CATHODE | STYLE 8:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. COMMON ANODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. NO CONNECTION<br>12. ANODE/CATHODE<br>13. ANODE/CATHODE<br>14. COMMON CATHODE |

| DOCUMENT NUMBER:                                                                                                                                                       | 98ASB42565B         Electronic versions are uncontrolled except when accessed directly from the Document Repository.           Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:                                                                                                                                                           | SOIC-14 NB                                                                                                                                                                                                     |  | PAGE 2 OF 2 |  |  |

| ON Semiconductor and M are trademarks of Semiconductor Components Industries II C dha ON Semiconductor or its subsidiaries in the United States and/or other countries |                                                                                                                                                                                                                |  |             |  |  |

ON Semiconductor and united states and/or other countries. LC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative