# SC1894 Serial Peripheral Interface Programming Guide

UG6343; Rev 3.1; 2/17

Abstract

This document provides the information necessary to develop the hose software to communicate with the SC1894 by way of the Serial Peripheral Interface (SPI).

# TABLE OF CONTENTS

| 1. Introduction                                                                                                                                | 6 |

|------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.1. Scope                                                                                                                                     | 6 |

| 1.2. Acronyms                                                                                                                                  | 6 |

| 1.3. Revision History                                                                                                                          | 7 |

| 1.4. References                                                                                                                                | 7 |

| 2. Hardware Interface                                                                                                                          |   |

| 2.1. SPI Bus Hardware                                                                                                                          |   |

| 2.2. LOADENB (Pin 60) For Firmware Upgrade                                                                                                     |   |

| 2.3. RESETN (Pin 49) to Reset SC1894                                                                                                           |   |

| 3. SPI Host Message Communication                                                                                                              |   |

| 3.1. Host Procedure for 4-Byte Message Communication                                                                                           |   |

| 3.1.1. MRB Read Transaction                                                                                                                    |   |

| 3.1.2. MRB Write Transaction                                                                                                                   |   |

| 3.1.3. RSR Read Command                                                                                                                        |   |

| 3.1.4. CHK Read Command<br>3.1.5. CHK Write Command                                                                                            |   |

| <ul><li>3.1.5. CHK Write Command</li><li>3.1.6. Read/Write Message Protocol</li></ul>                                                          |   |

| 3.2. SPI Message Read/Write Command Format                                                                                                     |   |

| 3.2.1. Host Message to Read 1-byte from the Scratch Memory                                                                                     |   |

| 3.2.2. Host Message to Read 2-bytes From the Scratch Memory                                                                                    |   |

| <ul><li>3.2.3. Host Message to Write 1-byte to the Scratch Memory</li><li>3.2.4. Host Message to Write 2-bytes to the Scratch Memory</li></ul> |   |

| 3.2.4. Flost Message to White 2-bytes to the Scratch Memory                                                                                    |   |

| 3.3. Special Commands                                                                                                                          |   |

| 3.4. Special SPI Commands for Smooth Mode Calibration                                                                                          |   |

| 3.5. Average of the Magnitudes of the Coefficients                                                                                             |   |

| 3.6. Examples of SPI Message Communication Commands                                                                                            |   |

| 3.6.1. To Read the FW Build LSB From Scratch                                                                                                   |   |

| 3.6.2. To Enable/Disable RFOUT                                                                                                                 |   |

| 3.6.3. To Clear Warnings                                                                                                                       |   |

| 3.6.4. Write MaxPWRCalParameters A                                                                                                             |   |

| 3.6.5. To Clear MaxPWRCalParameters B<br>3.6.6. To Read Cost Function Value                                                                    |   |

| 3.6.7. To Transfer ATE Calibration parameters from OTP to EEPROM                                                                               |   |

| 3.6.8. To Read Temperature IC                                                                                                                  |   |

| 3.6.9. To Read RFIN and RFFB PMU Values                                                                                                        |   |

| 4. Reprogramming the EEPROM                                                                                                                    |   |

| 4.1. EEPROM Mapping and Customer Configuration Parameters                                                                                      |   |

| 4.1.1. Frequency Range Configuration                                                                                                           |   |

| 4.1.2. External Clock Configuration                                                                                                            |   |

| 4.1.                |                                                              |    |

|---------------------|--------------------------------------------------------------|----|

| 4.1.<br>4.1.        | 5 T ,                                                        |    |

| 4.1.                |                                                              |    |

| 4.1.                |                                                              |    |

| 4.1.<br>4.1.        | I I I I I I I I I I I I I I I I I I I                        |    |

| 4.1.                |                                                              |    |

| 4.1.                | 11. PDET Temperature Compensation Disabled                   | 47 |

| 4.1.                |                                                              |    |

| 4.1.                |                                                              |    |

|                     | EEPROM Write Instruction                                     |    |

| 4.3.                | EEPROM Read Instruction                                      |    |

|                     |                                                              |    |

|                     | Reading the Cost Function Variable                           |    |

|                     | Power Measurement Unit (PMU)                                 |    |

| <b>6.1.</b><br>6.1. | PMU Calibration Flow<br>1. PMU Scratch Parameters            |    |

| 6.2.                |                                                              |    |

|                     | TDD Considerations—Operation with < 100% Duty Cycle          |    |

| 6.3                 |                                                              |    |

| 6.3                 | .2. For Systems with a Variable Rx/Tx Duty Cycle             |    |

| 6.4.                | PMU EEPROM Parameters                                        |    |

| 7. De               | bug Features                                                 |    |

| 7.1.                | CCDF Parameters                                              |    |

| 7.2.                | Internal Temperature Sensor                                  |    |

| 7.3.                | Spectrum Reporting (SEM and PSD)                             |    |

| 7.3.<br>7.3.        |                                                              |    |

|                     | actory Calibration                                           |    |

|                     | Smooth Mode Calibration                                      |    |

| <b>8.1.</b><br>8.1. |                                                              |    |

| 8.1.                |                                                              |    |

| 9. I                | Example Code                                                 |    |

| 9.1.                | Set Frequency Range Example Code                             |    |

| 9.2.                | Get SPI Message Parameters Example Code                      |    |

| 9.3.                | SC1894 Clear Max PWR Cal Parameters Example Code (Optimized) |    |

| 9.4.                | SC1894 Set Max PWR Cal Parameters (Smooth Mode Calibration)  |    |

| 9.5.                | Read Cost Example Code                                       |    |

| 9.6.                | Read PMU CCDF Example Code                                   |    |

| 9.7.                | Set CCDF Mode Example Code                                   |    |

| 9.8.  | Get RFIN and RFFB PSD Example Code                     | 74   |

|-------|--------------------------------------------------------|------|

| 9.9.  | Read EEPROM Customer Configuration Parameters          | 76   |

| 9.10. | Convert 16-bit Signed Values from EEPROM Example Code  | . 79 |

| 9.11. | Convert 8-bit Signed Values from EEPROM Example Code   | . 79 |

| 9.12. | Convert 16-bit Signed Values from Scratch Example Code | . 79 |

# List of Figures

| Figure 1: Host SPI Connection for Multiple SC1894 Applications                             | 8  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2: Interface Connector for Development                                              | 8  |

| Figure 3: Single-Byte Read                                                                 |    |

| Figure 4: Single-Byte Write                                                                |    |

| Figure 5: Four-Byte Write                                                                  |    |

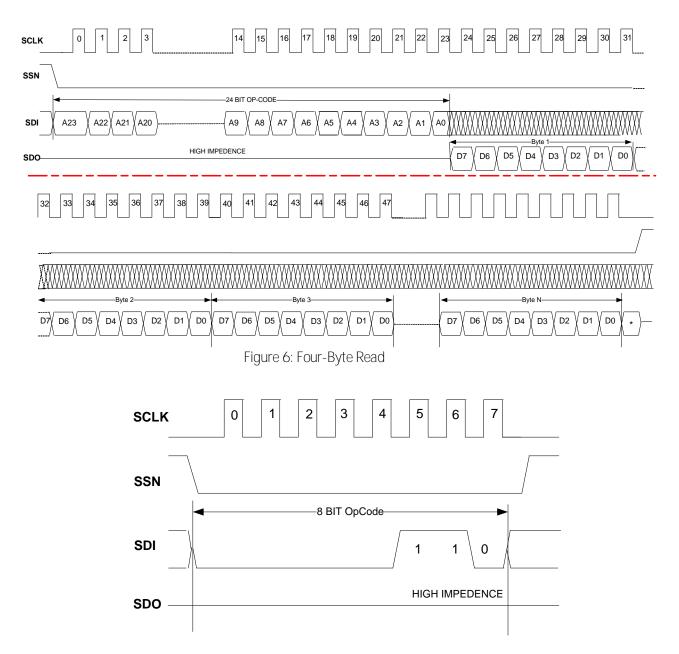

| Figure 6: Four-Byte Read                                                                   |    |

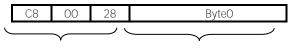

| Figure 7: SPI Special Command 06                                                           |    |

| Figure 8: Host Flow Diagram                                                                |    |

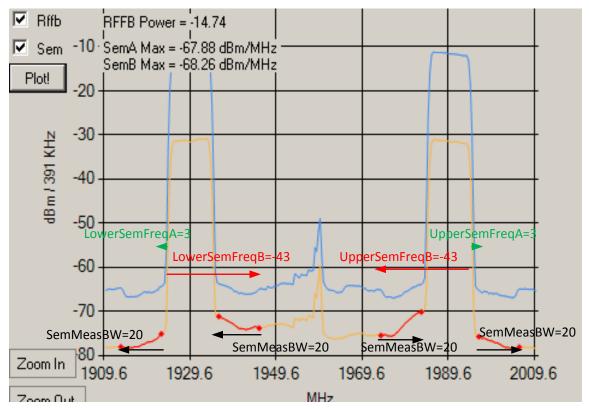

| Figure 9: Example of SEM Setting for Wideband Mode<br>for Two Separated LTE 10MHz Carriers |    |

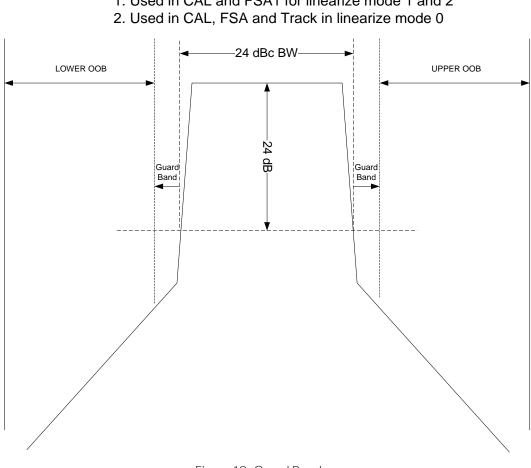

| Figure 10: Guard Band                                                                      |    |

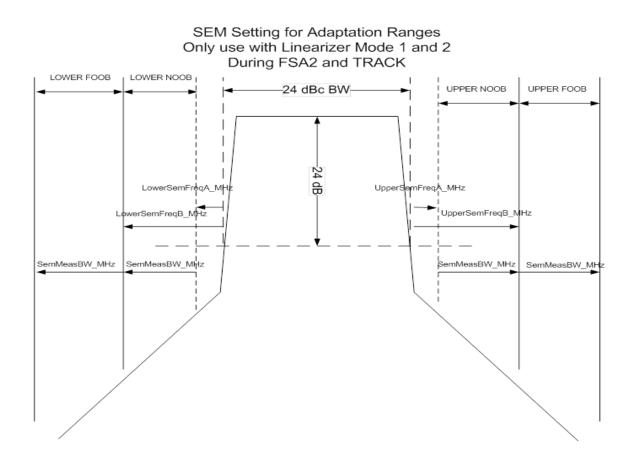

| Figure 11: NOOB and FOOB Definitions                                                       |    |

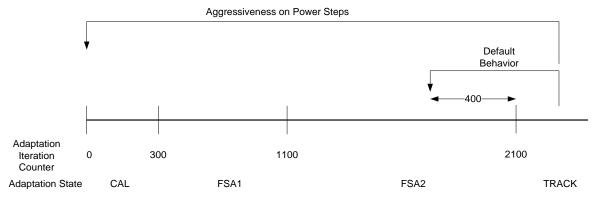

| Figure 12: Aggressiveness on Power Steps                                                   | 41 |

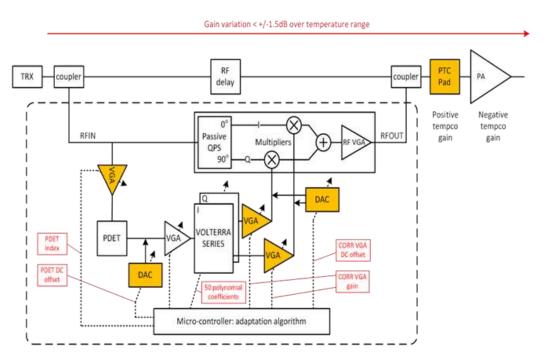

| Figure 13: SC1894 Correction Path Block Diagram                                            |    |

| Figure 14: PMU Calibration Flow                                                            |    |

| Figure 15: Smooth adaptation Calibration Procedure at Center Frequency A                   | 60 |

# List of Tables

| Table 1: Scratch Parameters Available Through SPI Messages                     |    |

|--------------------------------------------------------------------------------|----|

| Table 2: Special SPI Commands                                                  |    |

| Table 3: SPI Messages Communication Commands for Smooth Mode Calibration       |    |

| Table 4: Scratch Parameters for Smooth Calibration Command Status              |    |

| Table 5: EEPROM Mapping                                                        |    |

| Table 6: EEPROM Addresses for Customer Configuration Parameters                |    |

| Table 7: SC1894 Frequency Ranges                                               |    |

| Table 8: External Clock Configuration EEPROM Parameters                        |    |

| Table 9: External Clock Configuration values                                   |    |

| Table 10: Wideband Performance EEPROM Parameters                               |    |

| Table 11: SEM Parameters or Wideband Mode or Two Separated LTE 10 MHz Carriers |    |

| Table 12: EEPROM Parameters or Aggressiveness of Re-adaptation n Power Steps   |    |

| Table 13: Power Change Detection Trigger Parameters                            |    |

| Table 14: GaN PA Mode EEPROM Parameter                                         | 44 |

| Table 15: ATE Calibration Offset Zone Written EEPROM Parameter                 |    |

| Table 16: EEPROM Addresses for ATE Calibration Parameters                      | 45 |

| Table 17: OTP to EEPROM Transfer Special SPI Command                           |    |

| Table 18: PDET Compensation Flags                                              | 46 |

| Table 19: SC1894 EEPROM Endurance                                              | 51 |

| Table 20: Power Measurement Unit Scratch Parameters                            | 54 |

| Table 21: PMU EEPROM Parameter                                                 |    |

| Table 22: CCDF EEPROM Parameters                                               |    |

| Table 23: CCDF Scratch Parameters                                              |    |

| Table 24: Internal Temperature Sensor Scratch Parameters                       |    |

| Table 25: SEM EEPROM Parameters                                                |    |

| Table 26: SEM Scratch Parameters                                               |    |

| Table 27: PSD Scratch Parameters                                               |    |

# 1. Introduction

### 1.1. Scope

This document provides the information necessary to develop the host software to communicate with the SC1894 through the Serial Peripheral Interface (SPI).

| Acronyms | Description                                           |  |  |  |  |

|----------|-------------------------------------------------------|--|--|--|--|

| AGC      | Automatic Gain Control                                |  |  |  |  |

| CCDF     | Complementary Cumulative Distribution Function        |  |  |  |  |

| EEPROM   | Electrically Erasable, Programmable, Read-Only Memory |  |  |  |  |

| OTP      | One Time Programmable memory                          |  |  |  |  |

| EVB      | Evaluation Board                                      |  |  |  |  |

| EVK      | Evaluation Board Kit                                  |  |  |  |  |

| PAR      | Peak-to-Average Ratio                                 |  |  |  |  |

| PVT      | Process, Voltage and Temperature.                     |  |  |  |  |

| RF       | Radio Frequency                                       |  |  |  |  |

| RFFB     | RF Feedback                                           |  |  |  |  |

| RFIN     | RF Input                                              |  |  |  |  |

| RFOUT    | RF Output                                             |  |  |  |  |

| RFPAL    | RF PA Linearization                                   |  |  |  |  |

| SPI      | Serial Peripheral Interface                           |  |  |  |  |

| SSN      | SPI Slave Select Enable                               |  |  |  |  |

|          | Revision mistory                                                                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | Description                                                                                                                                                                                                                                                                                                                                              |

| 0.8      | Preliminary version based on firmware 4.0.02.11                                                                                                                                                                                                                                                                                                          |

| 1.0      | Based on firmware 4.0.05.00, Updated EEPROM mapping and added SPI commands for 1 or 2 point of smooth adaptation calibration                                                                                                                                                                                                                             |

| 2.0      | Based on firmware 4.1. Add all new features for SC1894-00, SC1894-13 and SC1894-23.                                                                                                                                                                                                                                                                      |

| 2.1      | Added Power Spectrum Density, Wideband and High PAR optimization parameters and updated example codes. Fixed minor formatting and typos.                                                                                                                                                                                                                 |

| 2.2      | Fixed RFIN_PeakPower_10ns and RFFB_PeakPower_10ns scratch addresses. Updated Smooth Calibration procedure to fix some issues and added example code. Updated Read/Write message protocol to add 5ms delay between RSR read commands.                                                                                                                     |

| 2.3      | Added new RFFB AGC index, fixed a few typos in addresses and variable size. Clarify calibration procedure. Added new parameters for GaN PA performance optimization, aggressiveness of re-adaptation on power steps and ATE Calibration offsets transfer from OTP to EEPROM.                                                                             |

| 2.4      | Fixed instructions to read cost function variable and Internal IC Temperature. Added Examples of SPI Message Communication Commands and Matlab example code to Read and plot RFIN and RFFB PSD.                                                                                                                                                          |

| 2.5      | Updated Read/Write message protocol. Added Examples of SPI Message Communication Commands to read RFIN and RFFB<br>PMU values. Updated EEPROM mapping to reflect bigger FW section. Added Smooth Mode Temperature and Gain<br>Compensation Discussion.                                                                                                   |

| 2.6      | Added extra information on GaN Mode.                                                                                                                                                                                                                                                                                                                     |

| 2.7      | Added back Get Output Status which was accidently removed in previous version.                                                                                                                                                                                                                                                                           |

| 3.0      | Added explanation of Lower Freeze Threshold parameter. Added description of Linearizer mode 2 and section on optimizing correction for meeting SEM specs close to carrier. Added description of power change detection trigger parameters. Removed features no longer supported. General edits to remove requirement for NDA to access SC1894 collateral |

| 3.1      | Fixed Table 18 and formatting issues.                                                                                                                                                                                                                                                                                                                    |

### 1.3. Revision History

### 1.4. References

| Document                                            |  |

|-----------------------------------------------------|--|

| SC1894 FW4.1.03.08 Quick Start Guide                |  |

| GUI Installation Guide                              |  |

| SC1894 Hardware Design Guide                        |  |

| SC1894 FW4.1.03.08 Release Notes                    |  |

| SC1894 Data Sheet                                   |  |

| SC1894 and PA System Design Power Budget Calculator |  |

| Microchip 25A512 Data Sheet                         |  |

# 2. Hardware Interface

### 2.1. SPI Bus Hardware

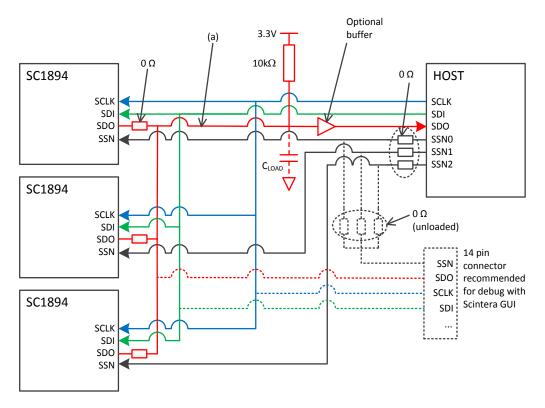

The SPI bus comprises four signals: SCLK, SSN, SDI and SDO. The SC1894 can only be used as a slave and the SPI clock can operate from 50KHz to 4MHz. The SPI bus can be shared with multiple slave devices (including several SC1894's). In this case, each slave must have a distinct Slave Select signal (SSN) from the host controller (see Figure 1). Refer to the "SC1894 Hardware Design Guide" for additional information.

Figure 1: Host SPI Connection for Multiple SC1894 Applications

IMPORTANT: It is highly recommended to use a 14-pin connector for debug with the GUI (see Figure 2) GUI only supports one SSN, so it is recommended to add a  $\Omega\Omega$  resistor as shown in Figure 1 to be able to debug with the GUI.

| WDTEN   | 1  | 2  | N/C    |

|---------|----|----|--------|

| LOADENB | 3  | 4  | STATO  |

| DGPt00  | 5  | 6  | RESETN |

| DGPIO1  | 7  | 8  | SSN    |

| GND     | 9  | 10 | SDI    |

| GND     | 11 | 12 | SDO    |

| GND     | 13 | 14 | SCLK   |

Figure 2: Interface Connector for Development

The SPI bus operates in Mode O (CPOL = 0 and CPHA = 0), which means that the data is sampled on the rising edge, and is generated on the falling edge, of SCLK. The signals use 3.3V digital CMOS levels. A detailed signal description is provided below:

- SCLK input: should receive a clock signal from the host during SPI transactions. The clock must have a 50% duty cycle. Internal to the SC1894, this pin is pulled down to ground through a 50KΩ resistor.

- SSN (Slave Select input) functions as an active-low slave selector. Internal to the SC1894, this pin is pulled up to DVDD33 by a 50K $\Omega$  resistor.

- SDI input: functions to receive addresses, messages/commands, and data values from the host. This signal should be wired to the MOSI (master out/slave in) signal from the Bus Master. Internal to the SC1894, this pin is pulled down to ground through a 50KΩ resistor.

- SDO three-state output: this signal should be wired to the host MISO signal (master in/slave out). This pin does not have an internal pullup/pulldown and must be externally pulled-up by a 10KΩ resistor to DVDD33. This pin is capable of driving 12mA. Below is the equation for determining the maximum load capacitance for the SDO pin:

- $C_{MAX}$  (shunt to ground) = 3.75e-4/f<sub>SPI</sub> (in Farad), where f<sub>SPI</sub> is the frequency of the SPI communication in Hz.

- For example: for  $f_{SPI} = 3MHz$ , the maximum load capacitance ( $C_{MAX}$ ) to ground is 125pF. The SC1894 SDO pin capacitance is 2.8pF and must be taken into account when calculating  $C_{MAX}$ .

- For values greater than C<sub>MAX</sub>, a buffer such as the NC7WZ16P6X would be required.

IMPORTANT: SSN should be disabled after each transaction as described below.

In addition to these pins, pin 49 (RESETN) and pin 60 (LOADENB) are required for:

- operating the GUI

- upgrading FW

- configuring the SC1894 from the host.

See sections 2.2 and 2.3 for additional details.

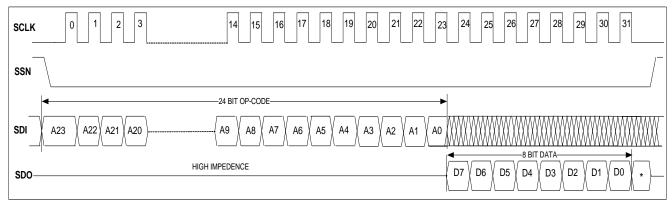

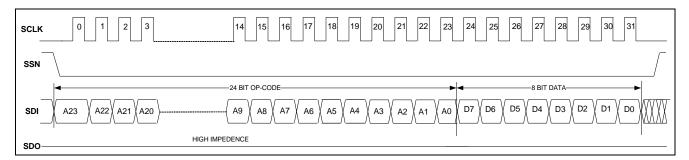

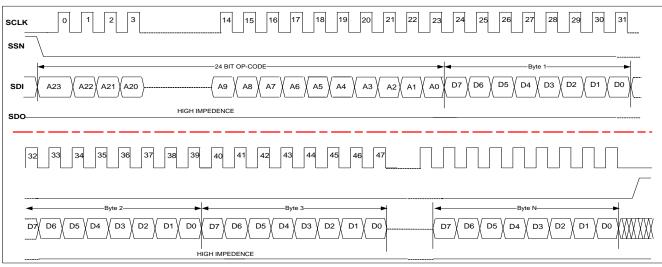

Figure 3 to Figure 7 illustrate examples of transactions used for SPI host message communication (section 3) or EEPROM read and write instructions (section 4).

See Microchip 25A512 data sheet 0 for additional details on transactions with the internal EEPROM.

Figure 3: Single-Byte Read

Figure 4: Single-Byte Write

Figure 5: Four-Byte Write

# 2.2. LOADENB (Pin 60) For Firmware Upgrade

LOADENB (pin 60) should be utilized when updating firmware. Input to the pin should be 3.3V CMOS level. Internally, this pin is pulled down to ground through a 50K $\Omega$  resistor. If the system has a host controller, it is recommended to connect this pin to one of its GPIO's. While this signal is set LOW, the SC1894 will be in normal operational mode. When the LOADENB signal is high, the SC1894 will be placed in a special mode where the SPI Bus is directly connected to the internally embedded EEPROM. In this mode, the SC1894 must be placed in a continuous reset mode by setting pin 49 (RESETN) to low. Throughout firmware updates, LOADENB must be at logic level high and. at the completion of the process, the signal must transition to logic level low. After the programming has been completed, a hard reset should be initiated by commanding the RESETN input low for at least 1µs, then toggled high.

### 2.3. RESETN (Pin 49) to Reset SC1894

It is required that RESETN, pin 49, be connected to a host processor through a GPIO connection or use a 1uF capacitor connected between pin 49 and ground. The RESETN pin is internally pulled-up to DVDD33 through a 50K $\Omega$  resistor. The RESETN (active-low) signal must be kept low for at least 100µs after the last supply is ramped to at least 90% of its final level; or it can be pulsed (from high to low, kept there for at least 1µs, and then back to high). When this signal is low, the SC1894 will be in a reset mode. When the signal goes high, the SC1894 will begin to boot-up and will complete this process in approximately 1 to 3 seconds (depending on the firmware version). After the boot-up process, SC1894 will start adapting towards optimal linearization.

Implementing a host GPIO connection to pin 49, RESETN allows the Host Processor to remotely reset the SC1894 if a re-initialization is required.

# 3. SPI Host Message Communication

The SC1894 requires a remote interface connection to configure critical parameters, like frequency range and min/max frequency scan bounds. In addition, this permits obtaining the operational status and error/warning information; critical for board startup and debugging. The SC1894 should either be connected to an external host or SPI connector to be able to use the GUI. This provides the following benefits:

- 1. Ability to download updated versions of SC1894 firmware with incremental feature sets.

- 2. Ability to obtain continuous operational status.

- 3. Ability to obtain error/warning alarms.

- 4. Ability to configure the SC1894 to the appropriate frequency range with the corresponding Min and Max Frequency scanning range limits.

In order to exchange information with the SC1894 internal memory over the SPI bus, the Host must follow the communication protocol described in the following sections.

### 3.1. Host Procedure for 4-Byte Message Communication

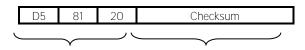

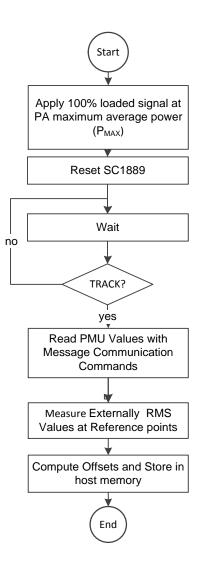

This section summarizes the Host procedure for 4-byte message communication. Refer to Figure 8 for the host flow diagram. Three types of registers are used in this message communication protocol.

- 1. MRB: 4-byte Message Reply Buffer

- 2. RSR: 1-byte Read Status Register

- 3. CHK: 1-byte Checksum Register

Five transmissions are required to read/write these registers.

### 3.1.1. MRB Read Transaction

This transaction consists of two parts. In the first part of the transaction, the Host sends an Opcode which indicates an MRB register read transaction. In the second part of the transaction, the SC1894 sends the 4 bytes of the MRB register. The total transaction length is 56 SCLK cycles. This transaction is described in Figure 8.

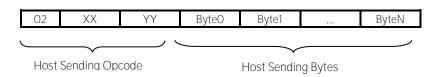

### 3.1.2. MRB Write Transaction

This transaction consists of two parts. In the first part, the Host sends the Opcode indicating a write transaction to MRB registers. In the second part of transaction, the Host sends 4 message bytes to be written to MRB registers. The total transaction length is 56 SCLK cycles. This transaction is described in Figure 8.

|   | FO | 00 | 20 | ByteO | Byte1 | Byte2 | Byte3 |

|---|----|----|----|-------|-------|-------|-------|

| Ľ |    |    | へ  | _     |       |       | )     |

Host Sending Opcode Host Sending Message Bytes

### 3.1.3. RSR Read Command

This transaction consists of two parts. In the first part of transaction, the Host sends the Opcode to read the RSR register. In the second part of the transaction, the SC1894 sends 1-byte which is the contents of the RSR register. The total transaction length is 32 SCLK cycles. Note that RSR is a read only register. This transaction is described in Figure 8.

Host Sending Opcode SC1894 Response

### 3.1.4. CHK Read Command

This transaction consists of two parts. In the first part of the transaction, the Host sends the Opcode to read the CHK register. In the second part of the transaction, the SC1894 sends the 1-byte content of the CHK register. The total transaction length is 32 SCLK cycles. This transaction is described in Figure 8.

| Ľ | D5 | 81     | 28 | ByteO |

|---|----|--------|----|-------|

|   |    | $\neg$ |    |       |

Host Sending Opcode SC1894 Response

### 3.1.5. CHK Write Command

In this transaction, the Host sends the Opcode to write the CHK register along with the checksum value. The total transaction length is 32 SCLK cycles. This transaction is described in Figure 8.

Host Sending Opcode Checksum

### 3.1.6. Read/Write Message Protocol

The following steps summarize the read/write message protocol:

- 1. Wait at least one second following reset before proceeding with step 2.

- 2. Host reads the RSR to determine current value.

- 3. Compose the four-byte message to write to the MRB, then compute the modulo-256 sum over these four bytes. Then compute the one's complement of the resulting value (i.e., invert each bit). The resulting value is the checksum for the message.

- 4. Write the checksum found in step 3 to the CHK register.

- 5. Write the four-byte message to the MRB. Start a timer with expiration value of one second upon completion of the write.

- 6. Host reads the RSR by using the RSR read command, C8 OO 28. Read byte can assume the following four values:

| RSR Value    | SC1894 Status                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OxOF or OxFO | RSR values 0x0F and 0xF0 alternate indicating that the SC1894 response to prior command is ready.<br>These values are also referred to as ACK0/1, respectively |

| OxFF         | RSR of 0xFF indicates the most recently issued command was not received correctly. This value is also referred to as a NAK.                                    |

| 0x00         | Indicates that the SC1894 has not yet completed processing of any commands since being reset                                                                   |

Host should keep polling the RSR every 5ms until either the timer expires or the RSR changes value. Any value other than the four in this table, is treated the same as a NAK.

- 1. If the expected ACK is returned before the timer expires, host reads the MRB registers by issuing an MRB read command, then read the CHK register by issuing a CHK read command. If timer expires before the RSR changes, or new RSR value is anything other than expected ACK, return to step 4.

- 2. Host computes the ones complement modulo-256 checksum over the five bytes consisting of the four bytes read from the MBR register plus the one byte from the RSR. Compare against the value read from the CHK register. If the values match, then transaction is complete. Otherwise, return to step 4.

IMPORTANT: After Reset, the first read byte of MRB will remain 0x00 until the first command response is available. The SSN should be disabled after each transaction as described above.

- Before sending a command, it is required to read the RSR.

- 1. If OxOF is read, then OxFO will indicate that the response to the command is ready.

- 2. Similarly, if OxFO was read before sending the command, then OxOF will indicate that the response of the command is ready.

- 3. If the chip was reset, then "0x00" will be read and either 0xF0 or 0x0F will indicate that the response to the command is ready.

Figure 8 provides a flow diagram that illustrates the sequence of actions from the start of a transaction to the completion.

See section 3.6 for examples of SPI Message Communication Commands.

Figure 8: Host Flow Diagram

#### SPI Message Read/Write Command Format 3.2.

SPI messages to read/write 1 or 2-byte are described in the following sections. These commands only allow accessing the first 4K bytes of the scratch memory. For some of the parameters, it is required to access address beyond the 4K limit. Then it is required to send a special command to extend the readable range.

3.2.1. Host Message to Read 1-byte from the Scratch Memory Host Message to read 1-byte from the scratch is

|--|

Host Message SC1894 Response

Where XYY is the hexadecimal address in the scratch and  $ZZ_1$  the 1-byte value read.

3.2.2. Host Message to Read 2-bytes From the Scratch Memory Host Message to read 2-bytes from the scratch is

| 6X YY 00 00 EX YY ZZ <sub>1</sub> ZZ <sub>2</sub> |

|---------------------------------------------------|

|---------------------------------------------------|

Host Message

SC1894 Response

Where XYY is the hexadecimal address in the scratch and  $ZZ_1 ZZ_2$  the 2-byte value read.

3.2.3. Host Message to Write 1-byte to the Scratch Memory Host Message to write 1-byte to the scratch is

| L | UA     | TT |     | 00 | 0^ | II | LL1 | 00 |

|---|--------|----|-----|----|----|----|-----|----|

|   | $\sim$ | VV | 77. | 00 | ov | VV | 77. | 00 |

Host Message SC1894 Response

Where XYY is the hexadecimal address in the scratch and ZZ<sub>1</sub> the 1-byte value written.

3.2.4. Host Message to Write 2-bytes to the Scratch Memory Host Message to write 2-bytes to the scratch is

| 2 | Х | ΥY            | ZZ1 | $ZZ_2$ | AX | ΥY | ZZ1 | ZZ <sub>2</sub> |

|---|---|---------------|-----|--------|----|----|-----|-----------------|

| _ |   | $\rightarrow$ |     | $\sim$ |    | -  |     |                 |

Host Message SC1894 Response

Where XYY is the hexadecimal address in the scratch and  $ZZ_1 ZZ_2$  the 2-byte value written.

### 3.2.5. Supported SPI Message Communication Commands

These SPI messages use the host message protocol described in section 1. Please refer to Figure 8 for Host Flow Diagram. See section 9.2 for example code for reading SPI message parameters.

| Table 1: Scratch Parameters Available | Through SPI Messages |

|---------------------------------------|----------------------|

|---------------------------------------|----------------------|

| Scratch Address<br>(Hex) | Size/Access | Variable Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 002                      | 8-bit R     | HW Version       | Get Hardware version.<br>SC1894 = 66 = 0x42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 003                      | 8-bit R     | FW Version       | Get Firmware version. Represents W.X.YY.ZZ where each<br>hexadecimal digit for W and X is separately displayed as a decimal<br>where a value 0x41 would be displayed as 4.1.YY.ZZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 004                      | 8-bit R     | Get FW Build MSB | Get Firmware build MSB. Represents W.X.YY.ZZ where YY is the value converted to ASCII decimal where a value WX = $0x41$ and YY = $03$ is displayed as $4.1.03.ZZ$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 005                      | 8-bit R     | Status           | The Host should Get Status at least every 2s and not faster than<br>every 100ms.<br>Bit#7 Error occurred if bit contains "1"<br>Bit#6 Warning occurred if bit contains "1"<br>Bit#5-0 contains value describing overall status:<br>000000 = INIT<br>000001 = FSA (Full Speed Adaptation)<br>000011 = TRACK (Tracking)<br>000110 = CAL (Calibrating)<br>001001 = PDET (Calibrating)<br>001001 = PDET (Calibrating)<br>0ther values not valid modes<br>If bit#7 is set, host should "Read Error" within 6s. SC1894 will<br>reset 6s after an error occurs. Error information will be lost after<br>reset.<br>If bit#6 is set, host should "Read Warning" and "Clear Warning". |

| 006                      | 8-bit R     | Error            | Host to read error code from SC1894. XX is the decimal error<br>number. OO means no error. Any other values mean that the chip<br>has an internal failure and should not typically happen.<br>Please refer to the release note for Error code.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 007                      | 8-bit R     | Warning          | Host to read warning code from SC1894. YY is the decimal warning number. Please refer to the release note for Warning code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 008                      | 8-bit RW    | Output Mode      | Output Mode<br>XX = 00 = RFOUT Disabled (Adaptation is frozen and<br>SC1894 is not linearizing the PA)<br>XX = 01 = "FW Control". This means RFOUT is enabled, by<br>default, but can be disabled by the firmware. For example, in CAL,<br>RFOUT Status is OFF, even if the mode is set to "FW Control".<br>Required: After changing Output Mode, send the "Activate<br>Outputs" messages to be effective. See Table 2                                                                                                                                                                                                                                                      |

| 00A                      | 8-bit R     | FW Build LSB     | Firmware Build LSB. Represents W.X.YY.ZZ where ZZ is the value converted to ASCII decimal where a value WX = $0x41$ , YY = $03$ and ZZ = $08$ is displayed as $4.1.03.08$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Scratch Address<br>(Hex) | Size/Access | Variable Name        | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 010                      | 8-bit R     | Frequency Range      | XX hexadecimal value of Frequency Range.<br>XX = 01: 225MHz - 260MHz<br>XX = 02: 260MHz - 520MHz<br>XX = 03: 225MHz - 960MHz<br>XX = 04: 520MHz - 1040MHz<br>XX = 05: 1040MHz - 2080MHz<br>XX = 05: 1040MHz - 2700MHz<br>XX = 06: 698MHz - 2700MHz<br>XX = 07: 1800MHz - 2700MHz<br>XX = 08: 2700MHz - 3500MHz<br>XX = 09: 3300MHz - 3800MHz |

| O11                      | 16-bit R    | MinFrequencyScan     | XX YY hexadecimal value of 2xMinFrequency Scan (MHz). For<br>example, XX YY = OE 10 corresponds to MinFrequency=<br>1800MHz. The MinFrequencyScan is the lowest frequency that<br>the SC1894 examines when searching for the signal center<br>frequency.                                                                                     |

| 013                      | 16-bit R    | MaxFrequencyScan     | XX YY hexadecimal value of 2 x MaxFrequency Scan (MHz). For<br>example, XX YY = 15 EO corresponds to MaxFrequencyScan =<br>2800MHz. The MaxFrequencyScan is the highest frequency that<br>the SC1894 examines when searching for the signal center<br>frequency.                                                                             |

| 017                      | 8-bit R     | Adaptation Mode      | XX hexadecimal value of Adaptation Mode<br>XX = 00 = Duty Cycled Feedback OFF (Default State)<br>XX = 01 = Duty Cycled Feedback ON (Not recommended for TDD<br>applications)                                                                                                                                                                 |

| 018                      | 16-bit R    | Signal Bandwidth     | XX YY hexadecimal value of 2xSignalBandwidth(MHz). For<br>example, XX YY = 00 1E corresponds to signal Bandwidth =<br>15MHz.                                                                                                                                                                                                                 |

| 01A                      | 16-bit R    | Center Frequency     | XX YY hexadecimal value of 2xFrequency(MHz). For example, XX<br>YY = 0F A3 corresponds to signal center Frequency = 2001.5MHz.                                                                                                                                                                                                               |

| 023                      | 8-bit RW    | Adaptation State     | XX hexadecimal value of Adaptation State<br>XX = 00 = Frozen (Freeze Adaptation)<br>XX = 01 = Running (Default state: Adaptation Running)                                                                                                                                                                                                    |

| 032                      | 8-bit R     | Get Output Status    | Get Output Status.<br>= 00 = RFOUT OFF (RFOUT disable: Adaptation is frozen and<br>SC1894 is not linearizing the PA) = 01 = RFOUT ON                                                                                                                                                                                                         |

| 033                      | 8-bit R     | Normalization_Factor | 8-bit unsigned value of Normalization Factor.<br>0x2A = 42. See section 0 for details.                                                                                                                                                                                                                                                       |

| 034                      | 16-bit R    | Unnormalized_Coeff   | 16-bit unsigned value of the un-normalized coefficient value. See section 0 for details.                                                                                                                                                                                                                                                     |

| 23C                      | 8-bit R     | RFIN AGC             | 8-bit unsigned value of RFIN AGC (PDET) value between 0 and 15                                                                                                                                                                                                                                                                               |

| 9C4                      | 8-bit R     | RFFB AGC             | 8-bit unsigned value of RFFB AGC value between 0 and 29                                                                                                                                                                                                                                                                                      |

IMPORTANT: If the Message is less than 4-bytes long, it is required that 4-bytes be sent before disabling the SSN (although the content of the additional bytes may not have any particular value). So, for 2-byte messages, it is required to add two dummy bytes. Similarly, if the Reply is fewer than 4-bytes long, it is required that all 4-bytes are received before disabling the SSN. So, for a 2-byte response, 2 extra bytes will be received and discarded.

After changing Output Mode, it required to send the "Activate Outputs" messages to be effective. See Table 2.

# 3.3. Special Commands Table 2: Special SPI Commands

| Message (Hex) | Reply (Hex) | Command Name                              | Description                                                                                                                                                                                                                                |

|---------------|-------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 03 00 00   | 90 03 00 00 | Clear Warning                             | Clears the Warning Code                                                                                                                                                                                                                    |

| 10 04 00 00   | 90 04 00 00 | Activate Output                           | Activate Output Mode. This command must be issued following a Set Output Mode command, described in above message                                                                                                                          |

| 10 05 00 00   | 90 05 00 00 | Request Rescan                            | Requests rescan for signal frequency. Not disruptive to PA linearization.                                                                                                                                                                  |

| 10 CD 00 00   | 90 CD 00 00 | Extend Scratch Readable<br>Access Enable  | Enables extended readable range of the scratch by<br>adding address offset of 0x800.<br>The instructions in sections 0 to 3.2.4 will then access<br>address XYZ + 0x800.                                                                   |

| 10 CE 00 00   | 90 CE 00 00 | Extend Scratch Readable<br>Access Disable | Disables extended readable range of the scratch by removing address offset of 0x800.                                                                                                                                                       |

| 10 FA 00 00   | 90 FA 00 00 | Wake-up                                   | When the Duty Cycled Feedback is ON, the SC1894<br>will be mostly powered down during the OFF time (1s).<br>This command will force SC1894 to power back up by<br>going back to ON state. The wake process takes about<br>1ms to complete. |

| 10 FB 00 00   | 90 fb 00 00 | OTP to EEPROM Transfer                    | Copies 128 bytes of OTP to ATE Calibration Offset<br>Zone of EEPROM. See section 4.1.9 for details.                                                                                                                                        |

# 3.4. Special SPI Commands for Smooth Mode Calibration

The SC1894 can operate in one of two modes: Smooth Mode and Optimized Mode. In Optimized Mode, the firmware will execute the full AGC routines to find the optimal settings for the various attenuators and amplifiers in the SC1894 hardware whenever the conditions change. For example, if the PA output power is stepped down several dB, the AGC routines will be rerun. This causes significant spectral distortion during the time it occurs, but the final correction performance will usually be the best achievable by the hardware. Optimized mode is therefore not suitable for dynamic operation. It is mainly intended for tuning PAs, and debugging performance issues. To switch to Smooth Mode, a calibration procedure is run. The procedure essentially involves applying a waveform, then issuing some SPI commands to the firmware. The full AGC routines are run and the values stored in EEPROM by the firmware. Once these calibration parameters have been written, the device is operating in Smooth Mode. In Smooth Mode, if some condition (such as PA output power or temperature) changes, the firmware estimates what the optimal values are for the various AGC indices for the new condition, rather than rerunning the full AGC routines. The final settings may not be optimal, but they will be close enough that performance is only slightly degraded relative to what would be achieved in Optimized mode. The main benefit is that there is little spectral disruption in dynamic conditions. If the calibration values in EEPROM are zeroed out, and the device reset, then it reverts back to Optimized Mode. The SPI commands used for Smooth Mode calibration are described in Table 3. Use of these commands is described in Section 8, with example code provided in sections 9.3 and 9.4.

# Table 3: SPI Messages Communication Commands for Smooth Mode Calibration

| Message (Hex) | Reply (Hex) | Command Name                | Description                                                                                                                                                                                                 |

|---------------|-------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 F3 00 00   | 90 F3 00 00 | Clear MaxPWRCalParameters A | Firmware to clear maximum power amplifier output<br>power calibration parameter and adaptation coefficients<br>in EEPROM for frequency A. Then read<br>MaxPWRClearOnGoing for command status. See Table 4   |

| 10 F4 00 00   | 90 F4 00 00 | Clear MaxPWRCalParameters B | Firmware to clear maximum power amplifier output<br>power calibration parameter and adaptation coefficients<br>in EEPROM for frequency B. Then read<br>MaxPWRClearOnGoing for command status. See Table 4   |

| 10 F5 00 00   | 90 F5 00 00 | Write MaxPWRCalParameters A | Firmware to write maximum power amplifier output<br>power calibration parameter and adaptation coefficients<br>in EEPROM for frequency A. Then read<br>MaxPwrCalAOngoing for command status.<br>See Table 4 |

| 10 F6 00 00   | 90 F6 00 00 | Write MaxPWRCalParameters B | Firmware to write maximum power amplifier output<br>power calibration parameter and adaptation coefficients<br>in EEPROM for frequency B. Then read<br>MaxPwrCalBOngoing for command status. See Table 4    |

### Table 4: Scratch Parameters for Smooth Calibration Command Status

| Scratch Address<br>(Hex) | Size/<br>Access | Variable Name      | Description                                                                                                                                                                         |

|--------------------------|-----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC3                      | UNIT8 R         | MaxPWRClearOnGoing | Flag used to indicate the execution status of the command "Clear<br>MaxPWRCalParameters"<br>Keep executing reads of this flag until a value of 0x00 is returned<br>by the SC1894.   |

| DC4                      | UNIT8 R         | MaxPwrCalAOngoing  | Flag used to indicate the execution status of the command "Write<br>MaxPWRCalParameters A"<br>Keep executing reads of this flag until a value of 0x00 is returned<br>by the SC1894. |

| DC6                      | UNIT8 R         | MaxPwrCalBOngoing  | Flag used to indicate the execution status of the command "Write<br>MaxPWRCalParameters B"<br>Keep executing reads of this flag until a value of 0x00 is returned<br>by the SC1894. |

## 3.5. Average of the Magnitudes of the Coefficients

#### In "FSA" and "TRACK" states, the average of the magnitudes of the coefficients is computed as follows: Average\_Coeff = Unnormalized\_Coeff/Normalization\_Factor;

Refer to Section 3.2 for instructions on how to get these parameters.

Example:

Unnormalized\_Coeff = 0x04 59 = 1113

Normalization\_Factor = 42

Then Average\_Coeff = 1113/42 = 26.5

# 3.6. Examples of SPI Message Communication Commands 3.6.1. To Read the FW Build LSB From Scratch

The following shows the different SPI transactions to read the FW Build LSB from scratch: FWBuildLSB = rfpal\_msgCmdRead(h, hex2dec('00A'), 0)

-> D5 81 20 B5 %CHK Write Command CHK = B5

-> C8 00 28 00 %Read RSR

<- FF FF FF OF % Value is OF

-> F0 00 20 40 0A 00 00 % Send command With MRB Write Transaction

% CHK Computation. Mod256(0x40+0XA) = 0x4A. CHK = 0xFF-0x4A = 0xB5

-> C8 00 28 00 %Read RSR

<- FF FF FF FO % Value is FO indicates that the response to the command is ready to be read

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF CO OA 08 00 %Response to Read FW Build LSB is 08

-> D5 81 28 00 %Read CHK to make sure it matches the computed CHK

<- FF FF FF 3D %Read CHK = 3D

% CHK computation. Mod256(0xF0+0xC0+0x0A+0x08+0) = 0xC2. CHK = 0xFF - 0xC2 = 0x3D FWBuildLSB = 8

### 3.6.2. To Enable/Disable RFOUT

To disable RFOUT, the following shows the different SPI commands:

err = SPImsgRfOutEnable(h, 0)

-> D5 81 20 F7 % Write CHK = 0xF7

-> C8 00 28 00 %Read RSR

<- FF FF FF FO %Value is FO

-> F0 00 20 00 08 00 00 % Send MRB Write Transaction to write '0' to Output Mode scratch variable

% CHK Computation. Mod256(0x0+0X8) = 0x8. CHK = 0xFF-0x8 = 0xF7

-> C8 00 28 00 %Read RSR

<- FF FF FF OF %Value is OF indicates that the response to the command is ready to be read

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF 80 08 00 00 %SC1894 response

-> D5 81 28 00 %CHK Read Command to verify response CHK

<- FF FF FF 68 % CHK = 0x68 is read

% CHK computation. Mod256(0x0F+ 0x80+0x08+0x00+0x00+0) = 0x97. CHK = 0xFF-0x97 = 0x68

-> D5 81 20 EB %Write Command CHK = OxEB

-> C8 00 28 00 %Read RSR

<- FF FF FF OF % Value is OF

-> F0 00 20 10 04 00 00 % Activate Output command is sent with MRB Write Transaction

% CHK Computation. Mod256(Ox10+OXO4+OxO0+OxO0) = Ox14. CHK = OxFF-Ox14 = OxEB

-> C8 00 28 00 %Read RSR

<- FF FF FO %Value is FO indicates that the response to the command is ready to be read

-> FO 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF 90 04 00 00 %SC1894 response

-> D5 81 28 00 %CHK Read Command to verify response CHK

<- FF FF FF 7B %CHK = 0x7B is read

%CHK computation. Mod256(0xF0+ 0x90+0x04+0x00+0x00+0) = 0x84. CHK = 0xFF-0x84 = 0x7B err = 0

To Set RFOUT to FW Control, the following shows the different SPI commands:

err = SPImsgRfOutEnable(h, 1)

-> D5 81 20 F6 %Write CHK = 0xF6

-> C8 00 28 00 %Read RSR

<- FF FF FF FO %Value is FO

-> F0 00 20 00 08 01 00 % Send MRB Write Transaction to write '1' to Output Mode scratch variable

-> C8 00 28 00 %Read RSR

<- FF FF FF OF %Value is OF indicates that the response to the command is ready to be read

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF 80 08 01 00 %SC1894 response to Output Mode write command

-> D5 81 28 00 %CHK Read Command to verify response CHK

<- FF FF FF 67 %CHK = 0x67 is read

% CHK computation. Mod256(0x0F+ 0x80+0x08+0x01+0x00+0) = 0x98. CHK = 0xFF-0x97 = 0x67

-> D5 81 20 EB %Write Command CHK = 0xEB

-> C8 00 28 00 %Read RSR

<- FF FF FF OF %Value is OF

-> F0 00 20 10 04 00 00 % Activate Output command is sent with MRB Write Transaction

-> C8 00 28 00 %Read RSR

<- FF FF FO %Value is FO indicates that the response to the command is ready to be read

-> F0 00 28 00 00 00 00 % MRB Read Transaction to read the response

<- FF FF FF 90 04 00 00 %4-byte SC1894 response

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value

<- FF FF FF 7B %CHK = 0x7B is read

%CHK computation. Mod256(0xF0+0x90+0x04+0x00+0x00)=0x84. CHK = 0xFF-0x84 = 0x7B err = 0

### 3.6.3. To Clear Warnings

err = rfpal\_msgSa(h,O3)

-> D5 81 20 EC %CHK Write Command

-> C8 00 28 00 %Read RSR

<- FF FF FF FO %Value is FO

-> F0 00 20 10 03 00 00 %Clear warning command is sent with MRB Write Transaction

-> C8 00 28 00 %Read RSR

<- FF FF FF OF %Value is OF indicates that the response to the command is ready to be read

-> F0 00 28 00 00 00 00 % MRB Read Transaction to read the response

<- FF FF FF 90 03 00 00 %4-byte SC1894 response

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value <- FF FF 5D %CHK = 0x5D is read

%CHK computation. Mod256(0x0F+ 0x90+0x03+0x00+0x00)=0xA2. CHK = 0xFF-0xA2 = 0x5D err = 0

To Clear MaxPWRCalParameters A

SC1894clearMaxPWRCalParameters(h, 0)

-> D5 81 20 FC %CHK Write Command

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR before sending Command. Waiting for FO for response to be ready

-> F0 00 20 10 F3 00 00 %Clear Max PWR Cal Parameters command

% Mod256(0x10+0xF3+0+0)=0x03. CHK = FF-0x03 = FC

-> C8 00 28 00 %Send RSR Read Command until FO is read

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %OF is read from RSR. Response not ready.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF FO % Value is FO, which means that the response to Command is ready

-> F0 00 28 00 00 00 00 %MRB Read

<- FF FF FF 90 F3 00 00 %SC1894 Command response 90 F3 00 00

-> D5 81 28 00 %CHK Read Command

<- FF FF FF 8C %CHK = 0x8C

% CHK computation. Mod256(0xF0+0x90+0xF3+0+0)=0x73. CHK = 0xFF-0x73 = 0x8C

-> D5 81 20 EF %Write CHK=0xEF for Command

-> C8 00 28 00 %Send RSR Read

<- FF FF FF FO %Value is OxFO

-> F0 00 20 4D C3 00 00 %Read MaxPWRClearOnGoing value with MRB Write Transaction

% Mod256(0x4D+0xC3+0+0)=0x10. CHK = FF-0x10 = EF is correct.

-> C8 00 28 00 %Send RSR Read

<- FF FF FF OF %Value is OF, which means that the response to Command is ready

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF CD C3 00 00 %SC1894 4-byte response to Command to Read MaxPWRClearOnGoing

% O means that "Clear MaxPWRCalParameters" Command is completed.

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value <- FF FF FF 60 % CHK = 0x60 is read

% CHK computation. Mod256(0x0F+ 0xCD+0xC3+0x00+0x00)=0x9F. CHK = 0xFF-0x9F = 0x60

### 3.6.4. Write MaxPWRCalParameters A

The following shows the different SPI transactions for the Write MaxPWRCalParameters A: rfpal\_msgSa(h,hex2dec('F5'))

-> D5 81 20 FA %Write CHK = FA

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %Value is FO

-> FO OO 20 10 F5 OO OO %Send "Write MaxPWRCalParameters A" command with MRB Write Transaction

-> C8 00 28 00 %RSR Read Command

<- FF FF OF %Value is OF, which means that the response to Command is ready

-> FO OO 28 OO OO OO 00 %MRB Read Transaction to read the SC1894 response

<- FF FF FF 90 F5 00 00 %SC1894 4-byte response to Command

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value

<- FF FF FF 6B %CHK = 0x6B is read

% CHK computation. Mod256(0x0F + 0x90 + 0xF5 + 0x00 + 0x00)=0x94. CHK = 0xFF - 0x94 = 0x6B ans = 0

Then it is required to read the MaxPwrCalAOngoing flag to make sure the "Write MaxPWRCalParameters A" command has been completed.

calAOngoingFlg = rfpal\_msgCmdRead(h,hex2dec('DC4'),0);

-> D5 81 20 EE %Write CHK = EE

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %Value is FO

-> F0 00 20 4D C4 00 00 %Read MaxPwrCalAOngoing value with MRB Write Transaction

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %Value is OF, which means that the response to Command is ready

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the SC1894 response

<- FF FF FF CD C4 01 00 %SC1894 4-byte response:

%1 means "Write MaxPWRCalParameters A" not complete yet.

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value <- FF FF 5E %CHK = 0x5E is read

%CHK computation. Mod256(0x0F+ 0xCD+0xC4+0x01+0x00)=0xA1. CHK = 0xFF-0xA1 = 0x5E

-> D5 81 20 EE %Write CHK = EE

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %Value is OF

-> F0 00 20 4D C4 00 00 %Read MaxPwrCalAOngoing value with MRB Write Transaction

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %Value is FO, which means that the response to Command is ready

-> FO OO 28 OO OO OO OO %MRB Read Transaction to read the SC1894 response

<- FF FF FF CD C4 00 00 %SC1894 4-byte response:

% 0 means "Write MaxPWRCalParameters A" is complete.

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value <- FF FF 7E %CHK = 0x7E is read

% CHK computation. Mod256(0xF0 + 0xCD + 0xC4 + 0x00 + 0x00) = 0x81. CHK = 0xFF-0x81 = 0x7E >> calAOngoingFlg = 0

IMPORTANT: It might be required to Read MaxPwrCalAOngoing several times as the Write MaxPWRCalParameters A could take 1-2s

### 3.6.5. To Clear MaxPWRCalParameters B

SC1894clearMaxPWRCalParameters(h, 1)

-> D5 81 20 FB %CHK Write Command

- -> C8 00 28 00 %RSR Read Command

- <- FF FF FF OF %Value is OF

- -> F0 00 20 10 F4 00 00 %Send Clear Cal Param B with MRB Write Transaction

- -> C8 00 28 00 %RSR Read Command

- <- FF FF FF OF %Value is OF. Response is not ready yet

- -> C8 00 28 00 %RSR Read Command

- <- FF FF FF FO %Value is FO. Response is ready

- -> FO OO 28 OO OO OO 00 % MRB Read Transaction to read the SC1894 response

- <- FF FF FF 90 F4 00 00 %SC1894 4-byte response

- -> D5 81 28 00 %CHK Read Command

<- FF FF FF 8B %CHK = 0x8B

% CHK computation. Mod256(0xF0 + 0x90 + 0xF4 + 0 + 0) = 0x74. CHK = 0xFF-0x74 = 0x8B

-> D5 81 20 EF %Write CHK = 0xEF for Command

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %Value is FO

-> F0 00 20 4D C3 00 00 %Read MaxPWRClearOnGoing value with MRB Write Transaction

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %Value is OF, which means that the response to Command is ready

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF CD C3 00 00 %SC1894 4-byte response to Command to Read MaxPWRClearOnGoing

%0 means that "Clear MaxPWRCalParameters" Command is completed.

-> D5 81 28 00 %CHK Read Command to verify response CHK with SC1894 4-byte response+RSR value <- FF FF 60 %CHK = 0x60 is read

% CHK computation. Mod256(0x0F+ 0xCD+0xC3+0x00+0x00)=0x9F. CHK = 0xFF-0x9F = 0x60

### 3.6.6. To Read Cost Function Value

Cost\_function\_bytes = double(rfpal\_msgCmdRead(h, hex2dec('20D'), 1))

-> D5 81 20 90 %CHK Write Command

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %Value of OF

-> F0 00 20 62 0D 00 00 %MRB Write to read 2-byte from @ 0x20D = 525

%CHK computation. 0x62 + 0xD + 0 + 0 = 0x6F = 111. CHK = dec2hex(255 - 111) = 0x90

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %Value of FO. SC1894 response to command is ready

-> F0 00 28 00 00 00 00 %MRB Read

<- FF FF FF E2 OD EA 68 %SC1894 Command response

-> D5 81 28 00 %CHK Read Command

<- FF FF FF CE %CHK from SC1894 Command response

% CHK computation. OxFO + OxE2 + OxOD + OxEA + Ox68 = Ox331. Mod256 = Ox31 = 49.

% CHK = dec2hex(255-49) = OxCE

Cost\_function\_bytes = 60008 = 0xEA68

Since OxEA68>7FFF Then Cost = 60008-65536 = -5528

3.6.7. To Transfer ATE Calibration parameters from OTP to EEPROM First, unlock the EEPROM:

rfpal\_eepromWriteStatus (h,O);

Then issue

rfpal\_msgSa(h,hex2dec('FB'));

-> D5 81 20 F4 %Write CHK = FA

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR before sending Command. Waiting for FO for response to be ready

-> FO OO 20 10 FB OO 00 % OTP to EEPROM Transfer Command with MRB Write command

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 OO 28 OO %RSR Read Command

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR. Response not ready. Waiting for FO for response to be ready

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %FO is read from RSR. Response is ready.

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF 90 FB 00 00 %SC1894 4-byte response to OTP to EEPROM transfer command

-> D5 81 28 00 %CHK Read Command

<- FF FF FF 84 %CHK = 0x84 is read

% CHK computation. Mod256(0xF0+ 0x90+0xFB+0x00+0x00)=0x7B. CHK = 0xFF-0x7B = 0x84

### 3.6.8. To Read Temperature IC

ic\_temp\_bit = uint16(rfpal\_msgCmdRead(h, hex2dec('23D'), 1));

IC\_temp = Read16B\_signed\_Scratch(ic\_temp\_bit);

-> D5 81 20 60 %Write CHK = 60

-> C8 00 28 00 %RSR Read Command

<- FF FF OF %OF is read from RSR before sending Command. Waiting for FO for response to be ready -> FO OO 20 62 3D OO OO %Read IC Temp parameter with MRB Write command

%CHK computation. 0x62+0x3D+0=0x9F. CHK=0xFF-0x9F=0x60

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %FO is read from RSR. Response is ready.

-> FO OO 28 OO OO OO 00 %MRB Read Transaction to read the response

<- FF FF FE 2 3D 00 28 %SC1894 response is 0x28 = 40C. See section 9.12 for negative temperature conversion.

-> D5 81 28 00 %CHK Read Command

<- FF FF FF C8 %CHK = OxC8 is read

% CHK computation. Mod256(0xF0 + 0xE2 + 0x3D + 0x00 + 0x28) = 0x37. CHK = 0xFF-0x37 = 0xC8

### 3.6.9. To Read RFIN and RFFB PMU Values

RFIN\_PMU\_bytes = double(rfpal\_msgCmdRead(h, hex2dec('247'), 1)) %Address 0x247 = 583 -> D5 81 20 56 %Write CHK = 56

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OO %O is read from RSR before sending Command as the chip was just Reset.

-> F0 00 20 62 47 00 00 %Read RFIN PMU parameter with MRB Write command

%CHK computation. 0x62+0x47+0+0=0xA9. CHK=0xFF-0xA9=0x56

-> C8 00 28 00 %RSR Read Command

<- FF FF FF OF %OF is read from RSR. Response is ready.

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF E2 47 09 99 %SC1894 4-byte response 0x0999 = 2457

-> D5 81 28 00 %CHK Read Command

<- FF FF FF 25 %CHK = 0x25 is read

% CHK computation. Mod256(0x0F+0xE2+ 0x47+0x09+0x99)=0xDA. CHK = 0xFF-0xDA = 0x25 RFIN\_PMU\_bytes = 2457 = 256\*0x09+0x99=256\*9+153

% See section 6.2 for conversion and sections 9.6 and 9.12 for Matlab example code

RFIN.RMS = 3.01\*Read16B\_signed\_Scratch(RFIN\_PMU\_bytes)/1024 = 7.2222 dBm

RFFB\_PMU\_bytes = double(rfpal\_msgCmdRead(h, hex2dec('245'), 1)) %Address 0x245 = 581

-> D5 81 20 58 %Write CHK = 58

-> C8 OO 28 OO %RSR Read Command

<- FF FF OF %OF is read from RSR before sending Command. Waiting for FO for response to be ready

-> F0 00 20 62 45 00 00 %Read RFFB PMU parameter with MRB Write command

%CHK computation. 0x62+0x45+0+0=0xA7. CHK=0xFF-0xA7=0x58

-> C8 00 28 00 %RSR Read Command

<- FF FF FF FO %FO is read from RSR. Response is ready.

-> F0 00 28 00 00 00 00 %MRB Read Transaction to read the response

<- FF FF FF E2 45 F2 C5 %SC1894 4-byte response 0xF2C5 = 62149

-> D5 81 28 00 %CHK Read Command

<- FF FF FF 31 %CHK = 0x31 is read

% CHK computation. Mod256(0xF0+0xE2+ 0x45+0xF2+0xC5)=0xCE. CHK = 0xFF-0xCE = 0x31 RFFB\_PMU\_bytes = 62149

% RFFB RMS Power (dBm/40ms) over a 40ms measurement window. Updated every 300ms

% See section 6.2 for conversion and sections 9.6 and 9.12 for Matlab example code

RFFB.RMS= 3.01\*Read16B\_signed\_Scratch(RFFB\_PMU\_bytes)/1024 = -9.9559dBm

# 4. Reprogramming the EEPROM

IMPORTANT: To reprogram the EEPROM with updated firmware and new customer configuration parameters, it is important to know the EEPROM mapping, as described in Table 5, as the firmware download must start at address 0x0000 and not go over 0XDFFF. Additionally, the EEPROM addresses for customer configuration parameters are listed in Table 6.

The same EEPROM read and write instructions described in sections 4.1.10 and 4.3 are used to upload new firmware or update the customer configuration parameters. See Microchip 25A512 data sheet for additional details on the EEPROM inside the SC1894.

IMPORTANT: The number of EEPROM erase/write cycles is limited to one million.

## 4.1. EEPROM Mapping and Customer Configuration Parameters

### Table 5: EEPROM Mapping

| EEPROM Addressed<br>(Hex) | Description                                                                                                                                            |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0000-DFFF                 | Download firmware, starting at address 0x0000<br>Note: Firmware size may be smaller.<br>IMPORTANT: Do not write in the range: (end of firmware):0xDFFF |  |

| E000-F77F                 | 00-F77F Unused. Reserved.                                                                                                                              |  |

| F780-F7FF                 | ATE Calibration Parameters. See 4.1.9 for details                                                                                                      |  |

| F800-FBFF                 | Reserved.                                                                                                                                              |  |

| FCOO-FFFF                 | Customer configuration parameters. See Table 6 for details.                                                                                            |  |

| EEPROM @ (Hex) | Size   | Variable Name                                           |                                                                                                                                                                                                                                                                                                                         |

|----------------|--------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|