# High Voltage, Isolated IGBT Gate Driver with Isolated Flyback Controller

**Data Sheet**

# ADuM4138

#### FEATURES

6 A (typical) peak drive output capability Internal turn off NFET, on resistance: <1  $\Omega$ Internal turn on PFET, on resistance:  $<1.2 \Omega$ 2 overcurrent protection methods **Desaturation detection** Split emitter overcurrent detection Miller clamp output with gate sense input **Isolated fault output Isolated temperature sensor readback Propagation delay Rising: 95 ns typical** Falling: 100 ns typical Minimum pulse width: 74 ns Operating junction temperature range: -40°C to +150°C VDD1 and VDD2 UVLO Minimum external tracking (creepage): 8.3 mm (pending) Safety and regulatory approvals 5000 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 VIORM = 849 VPEAK (reinforced/basic) **Qualified for automotive applications**

#### **APPLICATIONS**

MOSFET and IGBT gate drivers Photovoltaic (PV) inverters Motor drives Power supplies

#### **GENERAL DESCRIPTION**

The ADuM4138 is a single-channel gate driver optimized for driving insulated gate bipolar transistors (IGBTs). Analog Devices, Inc., *i*Coupler<sup>®</sup> technology provides isolation between the input signal and the output gate drive.

The Analog Devices chip scale transformers also provide isolated communication of control information between the high voltage

and low voltage domains of the chip. Information on the status of the chip can be read back from the dedicated outputs.

The ADuM4138 includes an isolated flyback controller, allowing simple secondary voltage generation.

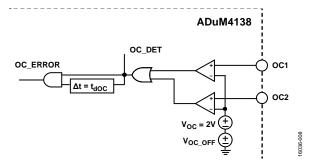

Overcurrent detection is integrated in the ADuM4138 to protect the IGBT in case of desaturation and/or overcurrent events. The overcurrent detection is coupled with a high speed, two-level turn off function in case of faults.

The ADuM4138 provides a Miller clamp control signal for a metal-oxide semiconductor field effect transistor (MOSFET) to provide IGBT turn off, with a single rail supply when the Miller clamp voltage threshold drops below 2 V (typical) above GND<sub>2</sub>. Operation with unipolar secondary supplies is possible with or without the Miller clamp operation.

A low gate voltage detection circuit can trigger a fault if the gate voltage does not rise above the internal threshold within the time allowed after turn on (12.8  $\mu$ s typical). The low voltage detection circuit detects IGBT device failures that exhibit gate shorts or other causes of weak drive.

Two temperature sensor pins, TS1 and TS2, allow isolated monitoring of system temperatures at the IGBTs. The secondary undervoltage lockout (UVLO) is set to 11.2 V (typical) in accordance with common IGBT threshold levels.

A serial peripheral interface (SPI) bus on the primary side of the device provides in field programming of temperature sensing diode gains and offsets to the ADuM4138. Values are stored on an electrically erasable programmable read-only memory (EEPROM) located on the secondary side of the device. In addition, programming is available for specific V<sub>DD2</sub> voltages, temperature sensing reporting frequencies, and overcurrent blanking times.

The ADuM4138 provides isolated fault reporting for overcurrent events, remote temperature overheating events, UVLO, thermal shutdown (TSD), and desaturation detection.

Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329. Other patents pending.

Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                                                     |

|------------------------------------------------------------------------------|

| Applications1                                                                |

| General Description                                                          |

| Revision History                                                             |

| Functional Block Diagram                                                     |

| Specifications                                                               |

| Electrical Characteristics 4                                                 |

| SPI Timing Specifications7                                                   |

| Package Characteristics7                                                     |

| Regulatory Information (Pending)8                                            |

| Insulation and Safety-Related Specifications8                                |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics (Pending)9 |

| Recommended Operating Conditions9                                            |

| Absolute Maximum Ratings10                                                   |

| Thermal Resistance                                                           |

| ESD Caution10                                                                |

| Pin Configuration and Function Descriptions11                                |

| Typical Performance Characteristics 12                                       |

#### **REVISION HISTORY**

| 8/2019—Rev. 0 to Rev. A                 |    |

|-----------------------------------------|----|

| Changes to Figure 1                     | 3  |

| Change to Overcurrent Detection Section |    |

| Changes to Figure 18                    | 19 |

| Changes to Figure 20                    |    |

| Changes to Figure 24                    | 21 |

| Changes to Figure 30                    | 23 |

12/2018—Revision 0: Initial Version

| Theory of | of Operation                           | 13 |

|-----------|----------------------------------------|----|

| Applicat  | ions Information                       | 14 |

| PCB L     | ayout                                  | 14 |

| Isolate   | ed Flyback Controller                  | 14 |

| SPI an    | d EEPROM Operation                     | 14 |

| User F    | Register Map                           | 15 |

| User F    | Register Bits                          | 15 |

| Config    | guration Register Bits                 | 15 |

| Contro    | ol Register Bits                       | 17 |

| Propa     | gation Delay Related Parameters        |    |

| Protec    | tion Features                          |    |

| Power     | Dissipation                            | 22 |

| Insula    | tion Lifetime                          | 22 |

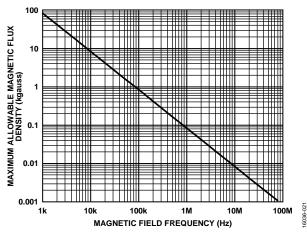

| DC C      | orrectness and Magnetic Field Immunity | 23 |

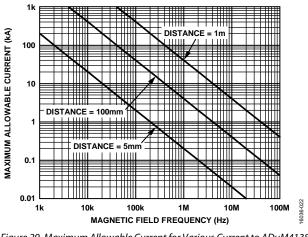

| Туріса    | l Application Circuit                  | 23 |

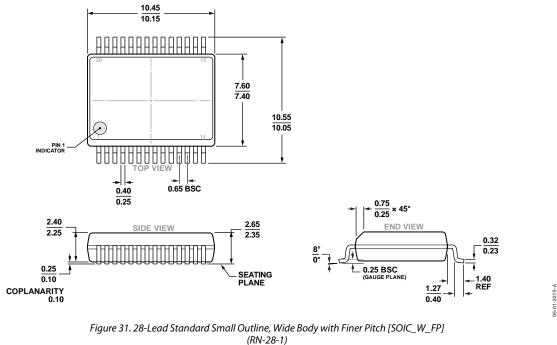

| Outline   | Dimensions                             | 24 |

| Order     | ing Guide                              | 24 |

| Auton     | notive Products                        | 24 |

|           |                                        |    |

8036-001

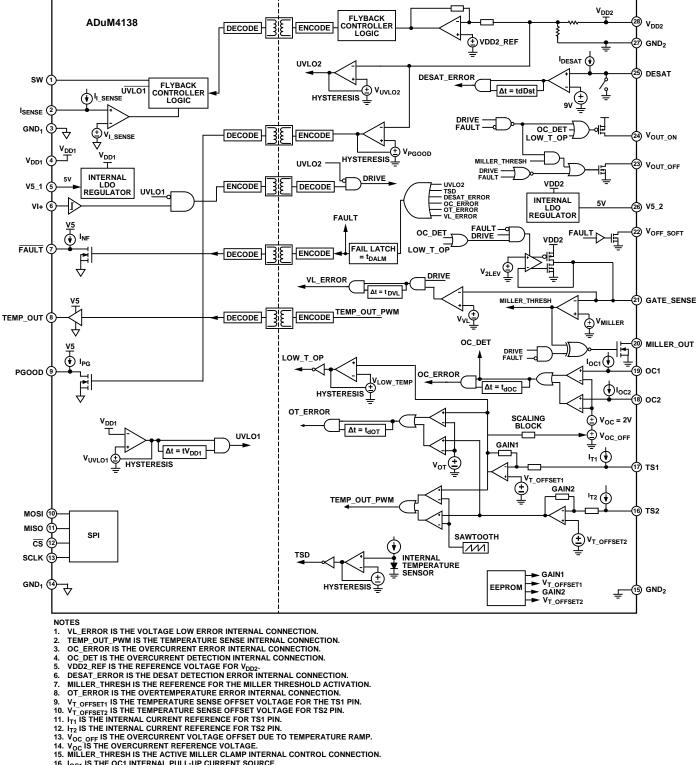

### FUNCTIONAL BLOCK DIAGRAM

- 15. MILLER\_THRESH IS THE ACTIVE MILLER CLAMP INTERNAL CONTROL CONNI 16.  $I_{OC1}$  IS THE OC1 INTERNAL PULL-UP CURRENT SOURCE. 17.  $I_{OC2}$  IS THE OC2 INTERNAL PULL-UP CURRENT SOURCE. 18.  $V_{PGOOD}$  IS THE PGOOD VOLTAGE REFERENCE. 19.  $V_{UVLO1}$  IS THE V<sub>DD1</sub> UVLO REFERENCE. 20.  $V_{LOW}$  TEMP IS THE LOW TEMPERATURE OPERATION REFERENCE. 21.  $V_{2LEV}$  IS THE TARGET VOLTAGE REFERENCE FOR TWO LEVEL OPERATION. 22. LOW\_T\_OP IS THE LOW TEMPERATURE OPERATION TRIGGER.

Figure 1.

### **SPECIFICATIONS ELECTRICAL CHARACTERISTICS**

Low-side voltages referenced to GND1 and high-side voltages referenced to GND2. VDD1 = 12 V, VDD2 = 16 V, TA = -40°C to +125°C, unless otherwise noted. All minimum and maximum specifications apply over the entire recommended operating junction temperature range, unless otherwise noted. All typical specifications are at  $T_A = 25^{\circ}$ C,  $V_{DD1} = 12$  V, and  $V_{DD2} = 16$  V, unless otherwise noted.

| Parameter                                          | Symbol                 | Min                     | Тур              | Max                     | Unit | Test Conditions/Comments                                                                                      |

|----------------------------------------------------|------------------------|-------------------------|------------------|-------------------------|------|---------------------------------------------------------------------------------------------------------------|

| DIGITAL CONVERTER SPECIFICATIONS                   |                        |                         |                  |                         |      |                                                                                                               |

| High-Side Power Supply                             |                        |                         |                  |                         |      |                                                                                                               |

| Input Voltage                                      | V <sub>DD2</sub>       | 12                      |                  | 25                      | V    | Operating without flyback                                                                                     |

| Input Current, Quiescent for $V_{\text{DD2}}$      | I <sub>DD2(Q)</sub>    |                         | 14               | 18                      | mA   | $TS1 = TS2 = open, VI+ = 0 V,$ $V_{DD2} = 25 V$                                                               |

| V5_2 Regulated Output Voltage<br>Isolated Flyback  | V5_2                   | 4.9                     | 5                | 5.1                     | V    |                                                                                                               |

| Soft Start                                         | tss                    |                         | 44               | 50                      | ms   |                                                                                                               |

| Output Voltage                                     | V <sub>FB</sub>        | V <sub>DD2</sub> – 2.6% | V <sub>DD2</sub> | V <sub>DD2</sub> + 2.5% | V    | All FLYBACK_V codes                                                                                           |

|                                                    |                        | 15.6                    | 16               | 16.4                    | V    | For FLYBACK_V code of 0111                                                                                    |

| Flyback Operating Frequency<br>Maximum             | fsw                    | 180                     | 200              | 220                     | kHz  |                                                                                                               |

| Duty Cycle                                         | D <sub>MAX</sub>       | 83.5                    | 86               | 90                      | %    |                                                                                                               |

| On Time                                            | t <sub>MAX</sub> ON    | 4.2                     | 4.8              | 5.4                     | μs   |                                                                                                               |

| Flyback Switch R <sub>DSON</sub>                   |                        |                         |                  |                         |      |                                                                                                               |

| Negative Channel Field Effect<br>Transistor (NFET) | Rdson_sw_n             |                         | 1.6              | 3.0                     | Ω    | SW current (I <sub>sw</sub> ) = 20 mA                                                                         |

| Positive Channel Field Effect<br>Transistor (PFET) | Rdson_sw_p             |                         | 1.7              | 2.8                     | Ω    | I <sub>sw</sub> = 20 mA                                                                                       |

| Logic Supply                                       |                        |                         |                  |                         |      |                                                                                                               |

| VDD1 Input Voltage                                 | V <sub>DD1</sub>       | 6.0                     |                  | 25                      | V    |                                                                                                               |

| V5_1 Regulated Output Voltage                      | V <sub>V5_1</sub>      | 4.9                     | 5.0              | 5.1                     | V    | No load                                                                                                       |

| VDD1 Input Current                                 | I <sub>DD1</sub>       |                         | 4.0              | 5.0                     | mA   | TS1 = TS2 = open, VI+ = 0 V,<br>TEMP_OUT and SW floating,<br>V <sub>DD1</sub> = 25 V, V <sub>DD2</sub> = 25 V |

| Logic Inputs (VI+, MOSI, SCLK, CS)                 |                        |                         |                  |                         |      |                                                                                                               |

| Input Current                                      | h                      |                         | 0.1              | 1.0                     | μΑ   |                                                                                                               |

| Input Voltage                                      |                        |                         |                  |                         |      |                                                                                                               |

| Logic High                                         | VIH                    | 2.5                     |                  |                         | V    |                                                                                                               |

| Logic Low                                          | VIL                    |                         |                  | 0.9                     | V    |                                                                                                               |

| Logic Input Hysteresis                             | V <sub>HYST</sub>      |                         | 1.10             |                         | V    |                                                                                                               |

| Logic Output                                       |                        |                         |                  |                         |      |                                                                                                               |

| MISO NFET RDSON                                    | Rdson_miso_n           |                         | 9                | 16                      | Ω    | MISO current ( $I_{MISO}$ ) = 5 mA                                                                            |

| MISO PFET RDSON                                    | Rdson_miso_p           |                         | 12.5             | 22                      | Ω    | I <sub>MISO</sub> = 5 mA                                                                                      |

| MISO PFET High-Z Leakage<br>UVLO                   | I <sub>MISO_LK_P</sub> |                         |                  | 20.0                    | μΑ   | MISO = 5 V                                                                                                    |

| Positive Going Threshold                           |                        |                         |                  |                         |      |                                                                                                               |

| V <sub>DD1</sub>                                   | VVDD1UV+               |                         | 4.25             | 4.5                     | V    |                                                                                                               |

| V <sub>DD2</sub>                                   | V <sub>VDD2UV+</sub>   |                         | 11.6             | 11.8                    | V    |                                                                                                               |

| Negative Going Threshold                           |                        |                         |                  |                         |      |                                                                                                               |

| V <sub>DD1</sub>                                   | V <sub>VDD1UV-</sub>   | 4.0                     | 4.13             |                         | V    |                                                                                                               |

| V <sub>DD2</sub>                                   | Vvdd2uv-               | 11.0                    | 11.2             |                         | V    |                                                                                                               |

| Hysteresis                                         |                        |                         |                  |                         |      |                                                                                                               |

| V <sub>DD1</sub>                                   | <b>V</b> VDD1UVH       |                         | 0.1              |                         | V    |                                                                                                               |

| V <sub>DD2</sub>                                   | V <sub>VDD2UVH</sub>   |                         | 0.3              |                         | V    |                                                                                                               |

## **Data Sheet**

## ADuM4138

| Parameter                             | Symbol                   | Min   | Тур   | Max    | Unit  | <b>Test Conditions/Comments</b>                       |

|---------------------------------------|--------------------------|-------|-------|--------|-------|-------------------------------------------------------|

| PGOOD                                 |                          |       |       |        |       |                                                       |

| Threshold Rising                      | V <sub>PGOOD_R</sub>     | 12.4  | 13.0  | 13.45  | V     | For FLYBACK_V code of 0000                            |

|                                       |                          | 17.3  | 18.2  | 18.8   | V     | For FLYBACK_V code of 1111                            |

| Threshold Falling                     | V <sub>PGOOD_F</sub>     | 11.77 | 12.3  | 12.75  | V     | For FLYBACK_V code of 0000                            |

|                                       |                          | 16.64 | 17.2  | 17.76  | V     | For FLYBACK_V code of 1111                            |

| Pull-Down NFET Resistance             | Rpgood_pd                |       | 14    | 24     | Ω     | PGOOD current (I <sub>PGSW</sub> ) =10 mA             |

| Pull-Up Current Source                | IPG                      | 66    | 78    | 88     | μΑ    | $PGOOD = 0 V, V_{DD1} = 12 V$                         |

| Filter Time                           |                          |       |       |        |       |                                                       |

| Active                                | tpgood_filt1             | 30    | 40    | 50     | μs    |                                                       |

| Cleared                               | tpgood_filt2             | 0.5   | 2.25  | 4      | μs    |                                                       |

| FAULT                                 |                          |       |       |        |       |                                                       |

| Pull-Down NFET Resistance             | RNFLT_PD_FET             |       | 16    | 28     | Ω     | $\overline{FAULT}$ current (I <sub>FT</sub> ) = 10 mA |

| Pull-Up Current Source                | I <sub>NF</sub>          | 66    | 78    | 88     | μA    | $\overline{FAULT} = 0 V, V_{DD1} = 12 V$              |

| Hold Time                             | t <sub>DALM</sub>        | 23.3  | 26.4  | 30.2   | ms    |                                                       |

| Low Gate Voltage                      |                          |       |       |        |       |                                                       |

| Reference Voltage                     | V <sub>VL</sub>          | 9.6   | 10    | 10.4   | v     |                                                       |

| Detect Delay Time                     | t <sub>DVL</sub>         | 10.3  | 12.8  | 15.6   | μs    |                                                       |

| Fault Delay Time                      | t <sub>DVL</sub> FLT     | 530   | 735   | 940    | ns    |                                                       |

| Overcurrent                           |                          |       |       |        |       |                                                       |

| Voltage                               |                          |       |       |        |       |                                                       |

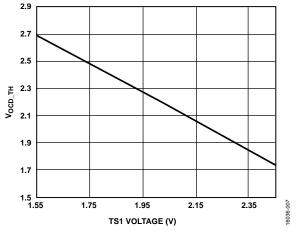

| Temperature, Disabled                 | V <sub>OCD TH</sub>      |       | 2     |        | v     | $T_RAMP_OP = 1$                                       |

| Temperature, Enabled                  | VOCD TH EN               | 2.59  | 2.69  | 2.76   | V     | $T_RAMP_OP = 0, TS1 = 1.55 V$                         |

|                                       | COCD_III_LIN             | 1.65  | 1.75  | 1.82   | v     | $T_RAMP_OP = 0, TS1 = 2.45 V$                         |

| Hysteresis                            |                          |       |       |        |       |                                                       |

| Temperature, Disabled                 | V <sub>OCD HYST</sub>    |       | 0.17  |        | v     | $T_RAMP_OP = 1$                                       |

| Temperature, Enabled                  | VOCD HYST EN             |       | 0.17  |        | V     | $T_RAMP_OP = 0, TS1 = 1.55 V$                         |

|                                       | COCD_INISI_EN            |       | 0.17  |        | v     | $T_RAMP_OP = 0, TS1 = 2.45 V$                         |

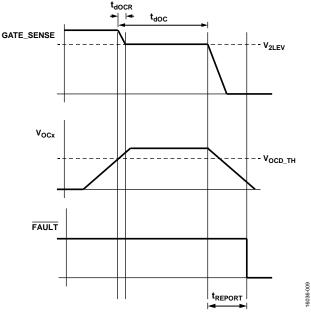

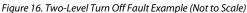

| Detect Delay Time                     | t <sub>dOC</sub>         | 520   | 920   | 1340   | ns    | $OC_2LEV_OP = 0, OC_TIME_OP =$                        |

| Fault Delay Time                      | t <sub>dOC FLT</sub>     | 510   | 735   | 960    | ns    | OC_2LEV_OP=1                                          |

| Detect Blanking                       | tBLANK                   | 0.275 | 0.36  | 0.47   | μs    | t <sub>BLANK</sub> bits = 0001                        |

| Pin Pull-Up Current Source            | loc                      | 3.8   | 5     | 6.2    | μA    | $V_{DD2} = 25 V, OC1 = OC2 = 0 V$                     |

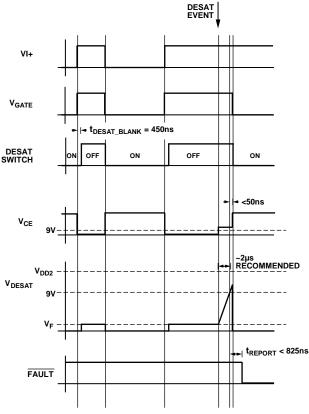

| Desaturation (DESAT) Detect           | .00                      | 0.0   | 5     | 0.2    | p., 1 |                                                       |

| Comparator Threshold                  |                          |       |       |        |       |                                                       |

| Rising                                | V <sub>DESAT_R</sub>     | 8.4   | 8.9   | 9.4    | V     |                                                       |

| Falling                               | V <sub>DESAT_F</sub>     | 7.7   | 8.1   | 8.5    | V     |                                                       |

| Hysteresis                            | V <sub>DESAT_H</sub>     |       | 0.85  |        | v     |                                                       |

| Internal Current Source               | IDESAT                   | 365   | 490   | 570    | μA    | DESAT = 0 V                                           |

| Fault Delay Time                      | t <sub>DESAT_DELAY</sub> | 620   | 825   | 1030   | ns    |                                                       |

| FAULT Pin Blank Time                  | t <sub>desat_blank</sub> | 300   | 450   | 620    | ns    |                                                       |

| DESAT Pin Pull-Down Resistance        | R <sub>DSON_DESAT</sub>  |       | 14    | 28     | Ω     | DESAT current (I <sub>D</sub> ) = 10 mA               |

| TSD                                   |                          |       |       |        |       |                                                       |

| Primary Side TSD                      |                          |       |       |        |       |                                                       |

| Positive Edge                         | t <sub>TSD_POS1</sub>    |       | 154   |        | °C    |                                                       |

| Negative Edge                         | t <sub>TSD_NEG1</sub>    |       | 135   |        | °C    |                                                       |

| Secondary Side TSD                    |                          |       |       |        |       |                                                       |

| Positive Edge                         | t <sub>TSD_POS2</sub>    |       | 150   |        | °C    |                                                       |

| Negative Edge                         | t <sub>TSD_NEG2</sub>    |       | 130   |        | °C    |                                                       |

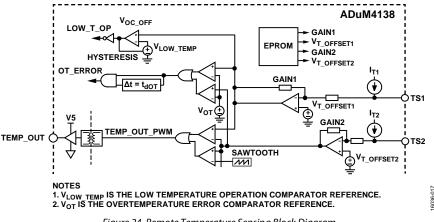

| Isolated Temperature Sensor           |                          |       |       |        |       |                                                       |

| Temperature Sense Bias Current Source | I <sub>T1</sub>          | 0.938 | 1.015 | 1.092  | mA    | TS1 = 2.2 V                                           |

|                                       | I <sub>T2</sub>          | 0.953 | 1.03  | 1.107  | mA    | TS2 = 2.2 V                                           |

| Temperature Sense Current Matching    | Іт_матсн                 |       | 0.014 | 0.0415 | mA    | TSx = 2.2 V                                           |

## ADuM4138

| Parameter                               | Symbol                          | Min   | Тур   | Max   | Unit | Test Conditions/Comments                                                      |

|-----------------------------------------|---------------------------------|-------|-------|-------|------|-------------------------------------------------------------------------------|

| Pulse-Width Modulation (PWM) Output     |                                 |       |       |       |      |                                                                               |

| Frequency                               | f <sub>PWM</sub>                | 9.20  | 10    | 10.80 | kHz  | $PWM_OSC = 0, TSx = 2.2 V$                                                    |

|                                         |                                 | 46    | 50    | 54    | kHz  | $PWM_OSC = 1, TSx = 2.2 V$                                                    |

| PWM Duty Cycle                          |                                 |       |       |       |      |                                                                               |

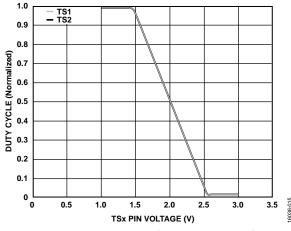

| TSx = 2.45 V                            |                                 | 7.50  | 10    | 11.3  | %    | $PWM_OSC = 0$                                                                 |

| TSx = 2.25 V                            |                                 | 26    | 28    | 29.5  | %    | $PWM_OSC = 0$                                                                 |

| TSx = 1.55 V                            |                                 | 90.2  | 92    | 93.3  | %    | $PWM_OSC = 0$                                                                 |

| TSx = 2.45 V                            |                                 | 7.5   | 10    | 11.5  | %    | PWMOSC = 1                                                                    |

| TSx = 2.25 V                            |                                 | 26    | 28    | 29.6  | %    | $PWM_OSC = 1$                                                                 |

| TSx = 1.55 V                            |                                 | 90.1  | 92    | 93.3  | %    | <br>PWM_OSC = 1                                                               |

| Overtemperature                         |                                 |       |       |       |      | _                                                                             |

| Detect Delay Time                       | t <sub>DOT</sub>                | 0.80  | 1     | 1.2   | ms   |                                                                               |

| Fault Delay Time                        | tdot flt                        | 530   | 735   | 940   | ns   |                                                                               |

| Detection Voltage                       |                                 |       |       | 2.0   |      |                                                                               |

| Rising                                  | V <sub>OT 0 R</sub>             | 1.62  | 1.69  | 1.73  | v    | OT_FAULT_SEL = 0                                                              |

|                                         | Vot_1_R                         | 1.63  | 1.73  | 1.81  | v    | OT_FAULT_SEL = 1                                                              |

| Falling                                 | V <sub>OT_0_F</sub>             | 1.57  | 1.65  | 1.70  | v    | $OT_FAULT_SEL = 0$                                                            |

| i uning                                 | Vot_1_F                         | 1.59  | 1.69  | 1.78  | v    | $OT_FAULT_SEL = 1$                                                            |

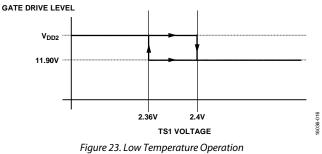

| Low Temperature Threshold               | V01_1_F                         | 1.59  | 1.09  | 1.70  | v    |                                                                               |

| Rising                                  | VLOW T R                        | 2.35  | 2.4   | 2.45  | v    | TS1 pin voltage                                                               |

| Falling                                 | VLOW T F                        | 2.31  | 2.36  | 2.41  | v    | TS1 pin voltage                                                               |

| TEMP_OUT Resistance                     | 2011_1_1                        |       |       |       |      |                                                                               |

| Pull-Down                               | R <sub>TEMP N</sub>             |       | 11.3  | 20    | Ω    | TEMP_OUT current ( $I_{\text{TEMP}_{OUT}}$ ) = 5 mA                           |

| Pull-Up                                 | RTEMP P                         |       | 13.7  | 23    | Ω    | $I_{\text{TEMP}}$ OUT = 5 mA                                                  |

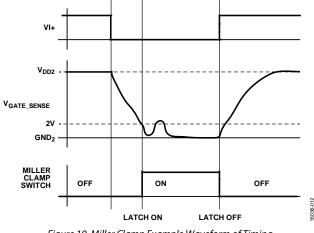

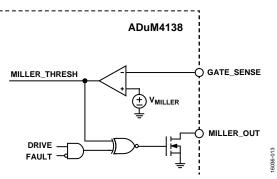

| Miller Clamp Voltage Threshold          |                                 | 1.9   | 2     | 2.1   | v    | Referenced to GND <sub>2</sub>                                                |

| Internal Turn Off NFET                  | • MILLER                        | 1.5   | -     | 2     | •    |                                                                               |

| On Resistance                           | R <sub>dson n</sub>             |       | 0.5   | 1     | Ω    | $V_{OUT_OFF}$ current ( $I_{VOUT_OFF}$ ) = 0.5 A,                             |

| on hesistance                           | NDSON_N                         |       | 0.5   | I     | 32   | $V_{DD1} = 6 V, V_{DD2} = 12 V$                                               |

| On Resistance 2 Level                   | Rdson_n_2lev                    |       | 1.8   | 4     | Ω    | $I_{VOUT_OFF} = 0.1 \text{ A}, V_{DD1} = 6 \text{ V}, V_{DD2} = 12 \text{ V}$ |

| Internal Turn On PFET                   |                                 |       |       |       |      |                                                                               |

| On Resistance                           | R <sub>DSON_P</sub>             |       | 0.6   | 1.2   | Ω    | $V_{OUT_ON}$ current ( $I_{VOUT_ON}$ ) = 0.5 A,                               |

|                                         |                                 |       |       |       |      | $V_{DD1} = 6 V, V_{DD2} = 12 V$                                               |

| On Resistance 2 Level                   | $R_{\text{DSON}_P_2\text{LEV}}$ |       | 2.0   | 4     | Ω    | $I_{VOUT_ON} = 0.1 \text{ A}, V_{DD1} = 6 \text{ V},$                         |

|                                         |                                 |       |       |       |      | $V_{DD2} = 12 V$                                                              |

| Miller Pull-Down NFET                   | Rdson_miller                    |       | 4.2   | 10    | Ω    | Miller current (I <sub>MILLER</sub> ) = 10 mA                                 |

| V <sub>OFF_SOFT</sub> R <sub>DSON</sub> | $R_{DSON\_SOFT\_OFF}$           |       | 15    | 36    | Ω    | $V_{OFF\_SOFT}$ current ( $I_{OFF\_SOFT}$ ) = 10 mA                           |

| Peak Current                            | ΙΡΕΑΚΙΡ                         |       | 6     |       | А    | $V_{DD2} = 15 V, 2 \Omega$ external resistance                                |

| Two-Level Plateau Voltage               | V <sub>2LEV</sub>               | 11.30 | 11.90 | 12.50 | V    |                                                                               |

| CURRENT LIMIT                           |                                 |       |       |       |      |                                                                               |

| Set Current                             | I <sub>L_SENSE</sub>            | 18    | 20    | 22    | μΑ   | $I_{\text{SENSE}} = 0.5 \text{ V}$                                            |

| Internal Current-Limit Reference        | V <sub>I_SENSE</sub>            | 480   | 500   | 520   | mV   | Rising edge                                                                   |

| Current-Limit Blanking Time             | t <sub>cl_blank</sub>           | 120   | 145   | 180   | ns   |                                                                               |

| SWITCHING SPECIFICATIONS                |                                 |       |       |       |      |                                                                               |

| Pulse Width <sup>1</sup>                | PW                              | 74    |       |       | ns   | No load, Miller clamp open                                                    |

| Propagation Delay                       |                                 |       |       |       |      |                                                                               |

| Rising <sup>2</sup>                     | t <sub>DLH</sub>                | 71    | 95    | 130   | ns   | No load, Miller clamp open                                                    |

| Falling <sup>2</sup>                    | t <sub>DHL</sub>                | 79    | 100   | 121   | ns   | No load, Miller clamp open                                                    |

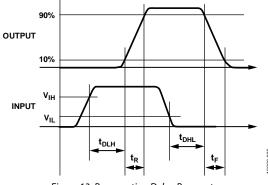

<sup>1</sup> The minimum pulse width is the shortest pulse width at which the specified timing parameter is guaranteed.

<sup>2</sup> to<sub>LH</sub> propagation delay is measured from the time of the input rising logic high threshold, Vi<sub>H</sub> to the output rising 0% level of the V<sub>OUT\_ON</sub> or V<sub>OUT\_OFF</sub> signal. to<sub>HL</sub> propagation delay is measured from the input falling logic low threshold, Vi<sub>L</sub> to the output falling 90% threshold of the V<sub>OUT\_ON</sub> or V<sub>OUT\_OFF</sub> signal. See Figure 13 for waveforms of propagation delay parameters.

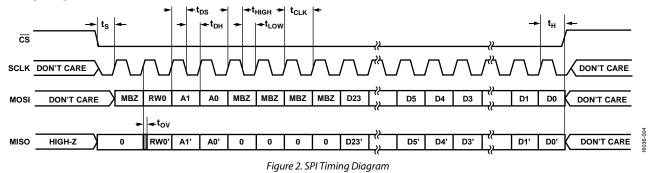

#### **SPI TIMING SPECIFICATIONS**

SPI timing specifications are guaranteed by design. All devices are production tested with 200 kHz SPI communication.

| Table 2.                |                          |     |     |     |      |

|-------------------------|--------------------------|-----|-----|-----|------|

| Parameter               | Description              | Min | Тур | Max | Unit |

| ts                      | Time to first clock edge | 8   |     |     | μs   |

| t <sub>DS</sub>         | Set period               | 1   |     |     | μs   |

| t <sub>DH</sub>         | Hold period              | 1   |     |     | μs   |

| <b>t</b> <sub>CLK</sub> | Clock period             | 5   |     |     | μs   |

| t <sub>H</sub>          | Release time             | 8   |     |     | μs   |

| thigh                   | Clock time high          | 100 |     |     | ns   |

| tLOW                    | Clock time low           | 100 |     |     | ns   |

| tov                     | Output valid time        |     |     | 240 | ns   |

#### SPI Timing Diagram

#### **PACKAGE CHARACTERISTICS**

Table 3.

| Parameter                                                 | Symbol           | Min | Тур              | Max | Unit |

|-----------------------------------------------------------|------------------|-----|------------------|-----|------|

| Resistance (Input Side to High-Side Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>12</sup> |     | Ω    |

| Capacitance (Input Side to High-Side Output) <sup>1</sup> | CI-O             |     | 2                |     | pF   |

| Input Capacitance                                         | Cı               |     | 4                |     | pF   |

<sup>1</sup> The device is considered a two terminal device: Pin 1 through Pin 14 are shorted together, and Pin 15 through Pin 28 are shorted together.

#### **REGULATORY INFORMATION (PENDING)**

#### Table 4.

| UL (Pending)                                       | CSA (Pending)                                                                       | VDE (Pending)                                                       | CQC (Pending)                                                |

|----------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------|

| UL1577 Component<br>Recognition Program            | Approved under CSA Component<br>Acceptance Notice 5A                                | DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12                      | Certified under<br>CQC11-471543-2012                         |

| Single Protection, 5000 V rms<br>Isolation Voltage | CSA 60950-1-07+A1+A2 and<br>IEC 60950-1, second edition, +A1+A2:                    | Reinforced insulation, 849 $V_{PEAK}$ ,<br>$V_{IOTM} = 8 kV_{PEAK}$ | GB4943.1-2011                                                |

|                                                    | Basic insulation at 830 V rms<br>(1174 V <sub>PEAK</sub> )                          |                                                                     | Basic insulation, 830 V rms $(1174 V_{PEAK})$                |

|                                                    | Reinforced insulation at 415 V rms (587 V <sub>PEAK</sub> )                         |                                                                     | Reinforced insulation,<br>415 V rms (587 V <sub>PEAK</sub> ) |

|                                                    | IEC 60601-1 Edition 3.1:                                                            |                                                                     |                                                              |

|                                                    | Basic insulation (1 MOPP),<br>519 V rms (734 V <sub>PEAK</sub> )                    |                                                                     |                                                              |

|                                                    | Reinforced insulation (2 MOPP),<br>261 V rms (369 V <sub>PEAK</sub> )               |                                                                     |                                                              |

|                                                    | CSA 61010-1-12 and IEC 61010-1 third edition                                        |                                                                     |                                                              |

|                                                    | Basic insulation, 300 V rms mains,<br>830 V secondary (1174 V <sub>PEAK</sub> )     |                                                                     |                                                              |

|                                                    | Reinforced insulation, 300 V rms<br>mains, 415 V secondary (587 V <sub>PEAK</sub> ) |                                                                     |                                                              |

| File E214100                                       | File 205078                                                                         | File 2471900-4880-0001                                              | File (pending)                                               |

#### INSULATION AND SAFETY-RELATED SPECIFICATIONS

#### Table 5.

| Parameter                                                                      | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                         |

|--------------------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                            |         | 5000  | V rms  | 1 minute duration                                                                                                                |

| Minimum External Air Gap (Clearance)                                           | L (I01) | 8.3   | mm min | Measured from input terminals to output terminals, shortest distance through air                                                 |

| Minimum External Tracking (Creepage)                                           | L (I02) | 8.3   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                             |

| Minimum Clearance in the Plane of the Printed<br>Circuit Board (PCB Clearance) | L (PCB) | 8.7   | mm min | Measured from input terminals to output<br>terminals, shortest distance through air,<br>line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                      |         | 0.017 | mm min | Insulation distance through insulation                                                                                           |

| Tracking Resistance (Comparative Tracking Index)                               | СТІ     | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                      |

| Material Group                                                                 |         | II    |        | Material group (DIN VDE 0110, 1/89, Table 1)                                                                                     |

#### DIN V VDE V 0884-10 (VDE V 0884-10):2016-12 INSULATION CHARACTERISTICS (PENDING)

These isolators are suitable for reinforced isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data. The asterisk (\*) marking on the package denotes DIN V VDE V 0884-10 approval for a 560  $V_{PEAK}$  working voltage.

#### Table 6. VDE Characteristics

| Description                                                 | Test Conditions/Comments                                                                                                                                                 | Symbol      | Characteristic | Unit  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-------|

| Installation Classification per IEC 60664-1                 |                                                                                                                                                                          |             |                |       |

| For Rated Mains Voltage ≤ 150 V rms                         |                                                                                                                                                                          |             | l to IV        |       |

| For Rated Mains Voltage ≤ 300 V rms                         |                                                                                                                                                                          |             | l to IV        |       |

| For Rated Mains Voltage ≤ 600 V rms                         |                                                                                                                                                                          |             | l to IV        |       |

| Climatic Classification                                     |                                                                                                                                                                          |             | 40/125/21      |       |

| Pollution Degree per DIN VDE 0110, Table 1                  |                                                                                                                                                                          |             | 2              |       |

| Maximum Working Insulation Voltage                          |                                                                                                                                                                          | VIORM       | 849            | VPEAK |

| Input to Output Test Voltage, Method B1                     | $      V_{\text{IORM}} \times 1.875 = V_{\text{pd(m)}}, 100\% \text{ production test}, \\       t_{\text{ini}} = t_m = 1 \text{ sec, partial discharge} < 5 \text{ pC} $ | $V_{pd(m)}$ | 1592           | Vpeak |

| Input to Output Test Voltage, Method A                      | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec,<br>partial discharge < 5 pC                                                                      | $V_{pd(m)}$ |                |       |

| After Environmental Tests Subgroup 1                        |                                                                                                                                                                          |             | 1274           | VPEAK |

| After Input and/or Safety Test<br>Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec,<br>partial discharge < 5 pC                                                                      |             | 1019           | Vpeak |

| Highest Allowable Overvoltage                               |                                                                                                                                                                          | VIOTM       | 8000           | VPEAK |

| Impulse                                                     | 1.2 μs rise time, 50 μs, 50% fall time in air to the preferred sequence                                                                                                  | VIMPULSE    | 8000           | Vpeak |

| Surge Isolation Voltage Basic                               | $V_{PEAK} = 12.8$ kV, 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time                                                                                                   | VIOSM       | 9800           | VPEAK |

| Surge Isolation Voltage Reinforced                          | $V_{PEAK} = 12.8$ kV, 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time                                                                                                   | VIOSM       | 8000           | VPEAK |

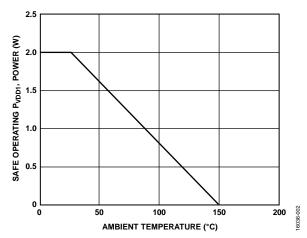

| Safety Limiting Values                                      | Maximum value allowed in the event of a failure (see Figure 3)                                                                                                           |             |                |       |

| Maximum Junction Temperature                                |                                                                                                                                                                          | Ts          | 150            | °C    |

| Total Power Dissipation at $T_A = 25^{\circ}C$              |                                                                                                                                                                          | Ps          | 2.0            | W     |

| Insulation Resistance at Ts                                 | Voltage between the input and output $(V_{IO}) = 500 V$                                                                                                                  | Rs          | >109           | Ω     |

Figure 3. Thermal Derating Curve, Dependence of Safety Limiting Values on Case Temperature, per DIN V VDE V 0884-10

#### **RECOMMENDED OPERATING CONDITIONS**

| Table /. |

|----------|

|----------|

| Parameter                                       | Value           |

|-------------------------------------------------|-----------------|

| Operating Junction Temperature Range            | -40°C to +150°C |

| Supply Voltages                                 |                 |

| V <sub>DD1</sub> Referenced to GND <sub>1</sub> | 6.0 V to 25 V   |

| V <sub>DD2</sub> Referenced to GND <sub>2</sub> | 12 V to 25 V    |

### ABSOLUTE MAXIMUM RATINGS

#### Table 8.

| Table 0.                                                 |                                    |

|----------------------------------------------------------|------------------------------------|

| Parameter                                                | Rating                             |

| Supply Voltages                                          |                                    |

| V <sub>DD1</sub>                                         | -0.2 V to +30 V                    |

| V <sub>DD2</sub>                                         | -0.2 V to +30 V                    |

| Primary Side Pins                                        |                                    |

| VI+, MOSI, <del>CS</del> , SCLK                          | –0.2 V to +5.5 V                   |

| SW, I <sub>SENSE</sub> , FAULT, TEMP_OUT,<br>PGOOD, MISO | -0.2 V to V5_1 + 0.2 V             |

| Secondary Side Pins                                      |                                    |

| TS1, TS2                                                 | -0.2 V to V5_2 + 0.2 V             |

| MILLER_OUT, VOFF_SOFT, VOUT_OFF                          | -0.2 V to + 30 V                   |

| Vout_on, DESAT, GATE_SENSE,<br>OC1, OC2                  | -0.2 V to V <sub>DD2</sub> + 0.2 V |

| Common-Mode Transients ( CM )                            | –150 kV/µs to +150 kV/µs           |

| Storage Temperature Range (Tst)                          | –55°C to +150°C                    |

| Operating Junction Temperature<br>Range                  | –40°C to +150°C                    |

| Electrostatic Discharge (ESD)                            |                                    |

| Human Body Model (HBM)                                   | ±1 kV                              |

| Charge Device Model (CDM)                                | ±1.25 kV                           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

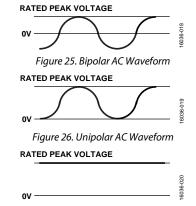

#### Table 10. Maximum Continuous Working Voltage<sup>1, 2, 3</sup>

#### Parameter Constraint Rating AC Voltage **Bipolar Waveform Basic Insulation** Lifetime limited by insulation lifetime per VDE-0884-11 849 V<sub>PEAK</sub> **Reinforced Insulation** 707 VPEAK Lifetime limited by insulation lifetime per VDE-0884-11 Unipolar Waveform **Basic Insulation** 1697 VPEAK Lifetime limited by insulation lifetime per VDE-0884-11 **Reinforced Insulation** 892 VPEAK Lifetime limited by package creepage per IEC 60664-1 DC Voltage **Basic Insulation** 1092 VPEAK Lifetime limited by package creepage per IEC 60664-1 **Reinforced Insulation** 546 VPEAK Lifetime limited by package creepage per IEC 60664-1

<sup>1</sup> See the Insulation Lifetime section for details.

<sup>2</sup> Other pollution degree and material group requirements yield a different limit.

<sup>3</sup> Some system level standards allow components to use the printed wiring board (PWB) creepage values. The supported dc voltage may be higher for those standards.

| Table 11 | . Truth T | able (Positi | ve Logic) |

|----------|-----------|--------------|-----------|

|----------|-----------|--------------|-----------|

| VI+ Input             | FAULT Pin             | V <sub>DD1</sub> State | V <sub>DD2</sub> State | GATE_SENSE Voltage (V <sub>GATE_SENSE</sub> ) |

|-----------------------|-----------------------|------------------------|------------------------|-----------------------------------------------|

| Low                   | High                  | Powered                | Powered                | Low                                           |

| High                  | High                  | Powered                | Powered                | High                                          |

| Don't Care or Unknown | Low                   | Powered                | Powered                | Low                                           |

| Don't Care or Unknown | Don't care or unknown | Unpowered              | Powered                | Low                                           |

| Don't Care or Unknown | Low                   | Powered                | Unpowered              | High-Z                                        |

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient thermal resistance, and  $\Psi_{JT}$  is the junction to top characterization parameter.

#### **Table 9. Thermal Resistance**

| Package Type <sup>1</sup> | θ」Α  | τ,Ψ  | Unit |

|---------------------------|------|------|------|

| RN-28-1                   | 62.4 | 2.97 | °C/W |

<sup>1</sup> 4-layer PCB.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

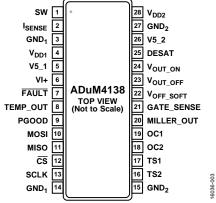

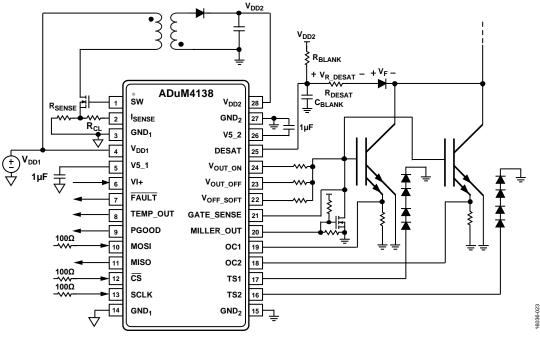

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 4. Pin Configuration

#### Table 12. Pin Function Descriptions

| Pin No. | Mnemonic              | Description                                                                                                                                                                                                                                                  |

|---------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SW                    | Switching Signal Pin for Isolated Flyback Converter. Connect this pin to the flyback transformer MOSFET.                                                                                                                                                     |

| 2       | I <sub>SENSE</sub>    | Flyback Current Sense. Current sense node for flyback transistor.                                                                                                                                                                                            |

| 3       | GND <sub>1</sub>      | Ground Reference for Primary Side. Decouple this pin to $V_{DD1}$ .                                                                                                                                                                                          |

| 4       | V <sub>DD1</sub>      | Input Supply Voltage Pin on Primary Side, 6 V to 25 V Referenced to GND1.                                                                                                                                                                                    |

| 5       | V5_1                  | 5 V Regulated Output. Connect this pin to a 1 μF external capacitor referenced to GND <sub>1</sub> . This pin controls the logic levels for the input pins.                                                                                                  |

| 6       | VI+                   | Noninverting Input for Gate Drive. Connect this pin to the incoming PWM control signal.                                                                                                                                                                      |

| 7       | FAULT                 | Fault Reporting Pin. The FAULT pin goes low when an overcurrent event is detected by the overcurrent pin, desaturation is detected, secondary UVLO occurs during thermal shutdown, during remote sensing overtemperature, or during gate voltage low errors. |

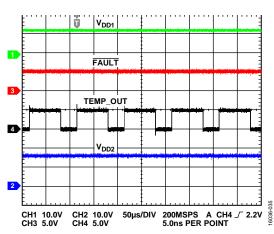

| 8       | TEMP_OUT              | Remote Temperature Sense Reporting Pin. This pin is 10 kHz or 50 kHz and is the 5% to 95% PWM output for the diode temperature sensor.                                                                                                                       |

| 9       | PGOOD                 | Power Good Pin. The signal is high when the output voltage is within regulation. When not in use, leave this pin open.                                                                                                                                       |

| 10      | MOSI                  | Master Out, Slave In Pin. This pin provides the MOSI connection for the SPI bus.                                                                                                                                                                             |

| 11      | MISO                  | Master In, Slave Out Pin. This pin provides the MISO connection for the SPI bus.                                                                                                                                                                             |

| 12      | CS                    | Chip Select for SPI Bus. Logic is active low.                                                                                                                                                                                                                |

| 13      | SCLK                  | Clock for SPI Bus. Connect this pin to the clock pin from the SPI master.                                                                                                                                                                                    |

| 14      | GND <sub>1</sub>      | Ground Reference for Primary Side.                                                                                                                                                                                                                           |

| 15      | GND <sub>2</sub>      | Secondary Ground Reference. Use this ground pin for the high current path.                                                                                                                                                                                   |

| 16      | TS2                   | Remote Temperature Sensor 2. Float or pull this pin high to V5_2 when not in use.                                                                                                                                                                            |

| 17      | TS1                   | Remote Temperature Sensor 1. See the Applications Information section for more information if this pin is unused.                                                                                                                                            |

| 18      | OC2                   | Split Emitter Overcurrent Detection 2. Connect this pin to GND <sub>2</sub> when this pin is not in use.                                                                                                                                                     |

| 19      | OC1                   | Split Emitter Overcurrent Detection 1. Connect this pin to GND <sub>2</sub> when this pin is not in use.                                                                                                                                                     |

| 20      | MILLER_OUT            | Output Signal to Control External MOSFET for Miller Clamping.                                                                                                                                                                                                |

| 21      | GATE_SENSE            | Miller Clamping Sense Pin. Connect this pin directly to the gate of the IGBT.                                                                                                                                                                                |

| 22      | V <sub>OFF_SOFT</sub> | Soft Shutdown Gate Connection. Connect this pin to the gate through the external series resistor. This pin pulls the gate down during fault conditions.                                                                                                      |

| 23      | Vout_off              | Turns Off Current Path Connection. Connect this pin to the gate through the external series resistor. This pin pulls the gate down during the low output command.                                                                                            |

| 24      | Vout_on               | Turns On Current Path Connection. Connect this pin to the gate through the external series resistor. This pin pulls the gate up during the high output command.                                                                                              |

| 25      | DESAT                 | Desaturation Detection Pin. Connect this pin to GND <sub>2</sub> when not in use.                                                                                                                                                                            |

| 26      | V5_2                  | 5 V Regulated Output on Secondary Side. Connect this pin to the 1 μF external capacitor referenced to GND <sub>2</sub> .                                                                                                                                     |

| 27      | GND <sub>2</sub>      | Ground Reference for Secondary Side.                                                                                                                                                                                                                         |

| 28      | V <sub>DD2</sub>      | Input Supply Voltage on Secondary Side, 15 V (Typical) Referenced to GND <sub>2</sub> .                                                                                                                                                                      |

## ADuM4138

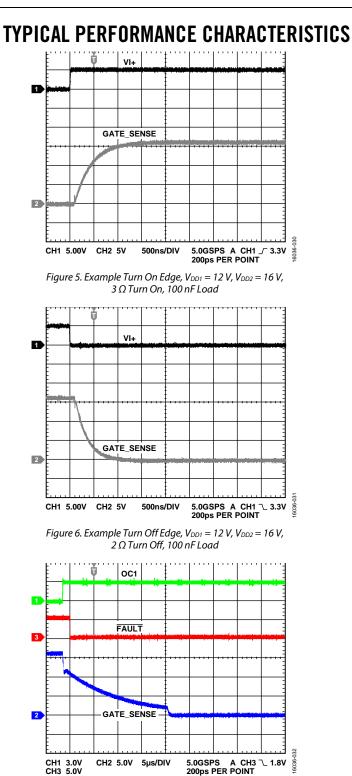

#### Figure 7. Example Overcurrent Fault, $V_{DD1} = 12 V$ , $V_{DD2} = 16 V$ , VI+ = 5 V, $2 \Omega$ Turn Off, 100 nF Load

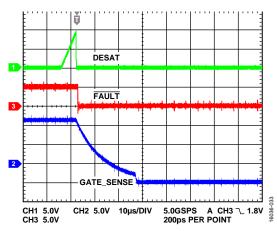

Figure 8. Example DESAT Fault,  $V_{DD1} = 12 V$ ,  $V_{DD2} = 16 V$ , VI+ = 5 V, 2  $\Omega$  Turn Off, 100 nF Load

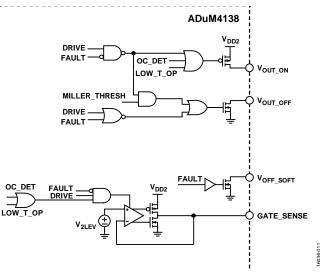

## THEORY OF OPERATION

Gate drivers are required in situations where fast rise times of switching device gates are required. The gate signals for enhancement power devices are referenced to a source or emitter node. The gate driver must follow this source or emitter node. As such, isolation is necessary between the controlling signal and the output of the gate driver in topologies where the source or emitter nodes swing, such as a half bridge. Gate switching times are a function of the drive strength of the gate driver. Buffer stages before a complementary metal-oxide semiconductor (CMOS) output reduce the total delay time and increase the final drive strength of the driver.

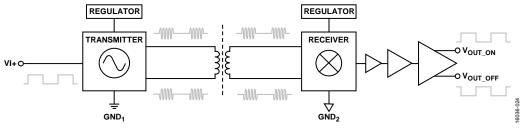

The ADuM4138 achieves isolation between the control side and the output side of the gate driver using a high frequency carrier that transmits data across the isolation barrier with *i*Coupler chip scale transformer coils separated by layers of polyimide isolation. The ADuM4138 uses positive logic on/off keying (OOK) encoding, in which a high signal is transmitted by the presence of the carrier frequency across the *i*Coupler chip scale transformer coils. Positive logic encoding ensures that a low signal is seen on the output when the input side of the gate driver is unpowered. A low state is the most common safe state in enhancement mode power devices and can drive in situations where shoot through conditions are present. The architecture of the ADuM4138 is designed for high common-mode transient immunity and high immunity to electrical noise and magnetic interference. Radiated emissions are minimized with a spread spectrum OOK carrier and differential coil layout. Figure 11 shows the OOK encoding used by the ADuM4138.

Figure 11. Operational Block Diagram of OOK Encoding

### APPLICATIONS INFORMATION PCB LAYOUT

The ADuM4138 IGBT gate driver requires no external interface circuitry for the logic interfaces. Power supply bypassing is required at the  $V_{DD1}$  and  $V_{DD2}$  supply pins. Use a small ceramic capacitor (>10  $\mu$ F) from  $V_{DD1}$  to GND<sub>1</sub>. Add at least 30  $\mu$ F to 60  $\mu$ F capacitance on the output power supply pin ( $V_{DD2}$ ) to provide the charge required to drive the gate capacitance at the outputs. This capacitance can be provided by multiple parallel capacitors. Avoid using vias on  $V_{DD2}$  on the bypass capacitor or employing multiple vias to reduce the inductance in bypassing because board vias can introduce parasitic inductance. The total lead length between both ends of the smaller capacitor and the input or output power supply pin must not exceed approximately 5 mm. For the 5 V regulators, place 1  $\mu$ F capacitors as close as possible to the ADuM4138.

#### ISOLATED FLYBACK CONTROLLER

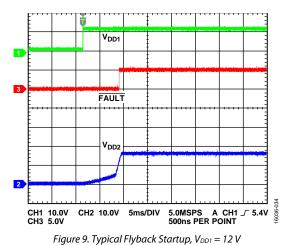

The ADuM4138 has an integrated isolated flyback controller that delivers isolated power to the gate being driven. The flyback controller provides a control signal to the flyback MOSFET on the low side of the device. This MOSFET switches the primary side of the flyback transformer. An external diode rectifies the secondary voltage and regulates the internal compensation on the secondary side. An inductive isolation link transfers duty cycle information to the primary side.

Startup includes a soft start, where the duty cycle is controlled to a maximum value that increases with time. The primary side has an oscillator that controls this timing. The secondary side also has an oscillator, creating the 200 kHz (typical) ramp signal used to create the PWM control. The handoff between the soft start and secondary oscillator is controlled internally without user intervention. An internal resistor network performs feedback sensing on the  $V_{DD2}$  pin.

The power good pin, PGOOD, is available for output on the primary side, allowing the user to observe when the secondary voltage is within regulation.

If  $V_{\rm DD2}$  loses power during operation, a fault posts to the primary side, and the flyback does not automatically attempt recovery. The  $V_{\rm DD1}$  power cycle initiates the flyback operation again.

Peak current mode control is employed on the primary side of the ADuM4138 through the I<sub>SENSE</sub> pin. Use the following equation to set the current limit:

$I_{PEAK} (mA) = 100 \text{ mV}/R_s$ (1)

where:

$I_{PEAK}$  is the desired peak current limit in mA.  $R_s$  is the sense resistor used to set the peak current limit in  $\Omega$ .

A typical application is shown in Figure 30. The recommended current-limit resistance ( $R_{CL}$ ) value is 20 k $\Omega$ . In operation, the equation for setting the peak current follows:

$$V_{I\_SENSE} = (I_{I\_SENSE}) \times (R_{CL}) + (I_{PEAK}) \times (R_S)$$

<sup>(2)</sup>

where:

$V_{I\_SENSE} = 500 \text{ mV} \text{ (typical)}$  $I_{I\_SENSE} = 20 \text{ } \mu\text{A} \text{ (typical)}$  $R_{CL} = 20 \text{ } k\Omega \text{ (recommended)}$

#### SPI AND EEPROM OPERATION SPI Programming

The ADuM4138 contains an SPI bus for setting remote temperature gains and offsets, PWM reporting frequency, high temperature faults, and low temperature operation mode. The SPI bus allows programming of the secondary side EEPROM, allowing a permanent operation setting. The SPI interface can operate in a daisy-chain mode to allow efficient use of the microcontroller input and output pins. When the chip select  $\overline{(CS)}$  pin is brought low, programming of the EEPROM is available. However, the gate drive output is disabled. The gate drive output is not available again until  $\overline{CS}$  is brought back to high.

Programming is performed using the standard SPI convention of clock polarity (CPOL) = 0 and clock phase (CPHA) = 1. The SPI timing diagram shown in Figure 2 demonstrates a typical read or write operation. Bit A1 and Bit A0 are the address bits. The must be zero (MBZ) bits must be set to 0. Bits[D23:D0] are the data bits, with MSB first. Bit RW0 sets whether the action is a read (0) or a write (1).

3036-005

#### **USER REGISTER MAP**

Figure 12 shows the user register map and binary addresses.

| ADDRESS | NAME    |    |                            |       |        |     |    |    |             |              |            |            | В        | ΙТ          |                          |     |       |            |       |   |   |      |           |         |   |

|---------|---------|----|----------------------------|-------|--------|-----|----|----|-------------|--------------|------------|------------|----------|-------------|--------------------------|-----|-------|------------|-------|---|---|------|-----------|---------|---|

| ADDRESS | NAWE    | 23 | 22                         | 21    | 20     | 19  | 18 | 17 | 16          | 15           | 14         | 13         | 12       | 11          | 10                       | 9   | 8     | 7          | 6     | 5 | 4 | 3    | 2         | 1       | 0 |

| 00      | USER    |    | o                          | FFSET | T_2[5: | :0] |    |    |             | GAIN         | 2[5:0      | ]          |          |             | OF                       | FSE | r_1[5 | :0]        |       |   |   | GAIN | 1[5:0     | ]       |   |

| 01      | CONFIG  |    | RESERVED                   |       |        |     |    |    | OT_FAULT_OP | OT_FAULT_SEL | OC_TIME_OP | OC_2LEV_OP | LOW_T_OP | OC_BLANK_OP | t <sub>BLANK</sub> [0:3] |     |       | ECC_OFF_OP | ACK_V |   |   |      | T_RAMP_OP | PWM_OSC |   |

| 10      | CONTROL |    | RESERVED RESERVED RESERVED |       |        |     |    |    |             | SIM_TRIM     |            |            |          |             |                          |     |       |            |       |   |   |      |           |         |   |

Figure 12. User Register Map

#### **USER REGISTER BITS**

Table 13 lists the user register (Address 00) bits and bit descriptions.

#### Table 13. User Register (Address 00) Bit Descriptions

| Bits    | Bit Name      | Description |

|---------|---------------|-------------|

| [23:18] | OFFSET_2[5:0] | TS2 offset  |

| [17:12] | GAIN_2[5:0]   | TS2 gain    |

| [11:6]  | OFFSET_1[5:0] | TS1 offset  |

| [5:0]   | GAIN_1[5:0]   | TS1 gain    |

#### OFFSET\_2[5:0] Bits

Use the OFFSET\_2 bits of the EEPROM to adjust the internal offset for the TS2 pin.

#### GAIN\_2[5:0] Bits

Use the GAIN\_2 bits of the EEPROM to adjust the internal gain for the TS2 pin.

#### OFFSET\_1[5:0] Bits

Use the OFFSET\_1 bits of the EEPROM to adjust the internal offset for the TS1 pin.

#### GAIN\_1[5:0] Bits

Use the GAIN\_1 bits of the EEPROM to adjust the internal gain for the TS1 pin.

#### **CONFIGURATION REGISTER BITS**

Table 14 lists the configuration (CONFIG) register (Address 01) bits and bit descriptions.

| Bit Name     | Bits    | Description                                                   |

|--------------|---------|---------------------------------------------------------------|

| Reserved     | [23:17] | Reserved                                                      |

| OT_FAULT_OP  | 16      | Overtemperature fault disable                                 |

| OT_FAULT_SEL | 15      | Overtemperature fault select                                  |

| OC_TIME_OP   | 14      | Disable two-level drive and timer<br>during overcurrent event |

| OC_2LEV_OP   | 13      | Overcurrent two-level operation select                        |

| LOW_T_OP     | 12      | Low temperature operation select                              |

| Bit Name                 | Bits   | Description                                                    |

|--------------------------|--------|----------------------------------------------------------------|

| OC_BLANK_OP              | 11     | Overcurrent blanking operation select                          |

| t <sub>blank</sub> [3:0] | [10:7] | Overcurrent blanking time                                      |

| ECC_OFF_OP               | 6      | Enable soft shutdown with error<br>correcting code (ECC) fault |

| FLYBACK_V[3:0]           | [5:2]  | Flyback output voltage setting                                 |

| T_RAMP_OP                | 1      | Overcurrent temperature ramp enable                            |

| PWM_OSC                  | 0      | Temperature reading output oscillator select                   |

#### OT\_FAULT\_OP Bit

Set the OT\_FAULT\_OP bit to 1 to disable a fault for overtemperature. If this bit is set to 0, the ADuM4138 issues a fault when the TS1 or TS2 pin detects an overtemperature event.

#### OT\_FAULT\_SEL Bit

The OT\_FAULT\_SEL bit selects between two overtemperature fault voltage thresholds. Set this bit to 0 to set the falling threshold to 1.65 V (typical) and the rising threshold is 1.69 V (typical). Set the OT\_FAULT\_SEL bit to 1 to set the falling threshold to 1.69 V (typical) and the rising threshold is 1.73 V (typical).

#### OC\_TIME\_OP Bit

Set the OC\_TIME\_OP bit to 1 to disable the two-level drive and timer during an overcurrent event. During an overcurrent event, the output immediately enters soft shutdown. If enabled, overcurrent blanking is still available.

#### OC\_2LEV\_OP Bits