#### CHANGE NOTIFICATION

November 02, 2015

Dear Sir/Madam: PCN# 110215

### Subject: Notification of Change to LTC4217

Please be advised that Linear Technology Corporation has made a change to the lead frame of the LTC4217 device to meet IPC/ JEDEC JSTD-020 Moisture Sensitivity Level 1 Classification. Moisture Sensitivity Level 1 classified devices can be shipped without dry pack with unlimited shelf life. Device with improved leadframe have longer moisture soak and more aggressive IR temp ramps.

The change includes adding an array of slot holes along the edge of the die attach paddle as mold locking feature to enhance mold adhesion mechanism to the lead frames. In addition to facilitate improvement in our manufacturing yield, a minor change was done to the datasheet as shown on the attached page of the marked up datasheet. The improved product with approximate date code of 1601 will be tested to the new limits.

Besides these changes, there was no change in form, fit, function, quality or reliability of the product. Similarly, there are no changes associated with the package footprint, PCB layout or product top marking, so the customer applications will be unaffected.

Parts incorporating the new lead frame design have been fully characterized and tested for package level reliability. The change was qualified by performing extensive characterization over the full operating voltage and temperature ranges and MSL1 preconditioning. Device with the new lead frame has been subjected to 1000 cycles of temperature cycles and thermal shock. Products built using the improved design will be shipped with a date code of approximately 1601.

Should you have any further questions or concerns please contact your local Linear Technology Sales person or you may contact me at 408-432-1900 ext. 2077, or by e-mail at <a href="mailto:jason.hu@linear.com">jason.hu@linear.com</a>. If I do not hear from you by January 4, 2016, we will consider this change to be approved by your company.

| Sincerely | , |

|-----------|---|

| Jason Hu  |   |

**Quality Assurance Engineer**

## LTC4217 Leadframe Design Improvement

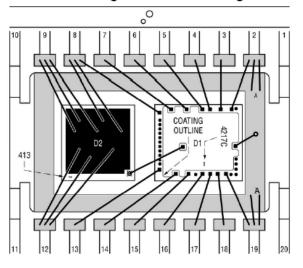

Existing Leadframe Design

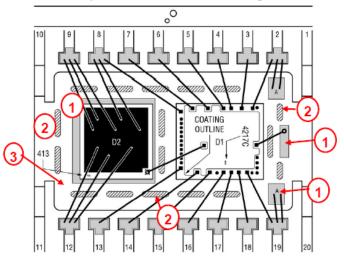

Improved Leadframe Design

- 1. Silver ring is replaced by spot silver on areas under FET die (D2), and for Rsense and down bond bonding to improve adhesion.

- 2. Half etched slots are added on the peripheral of die pad and between dies to enhance adhesion.

- 3. Brown oxide is added to die pad surface other than spot Ag areas to improve adhesion.

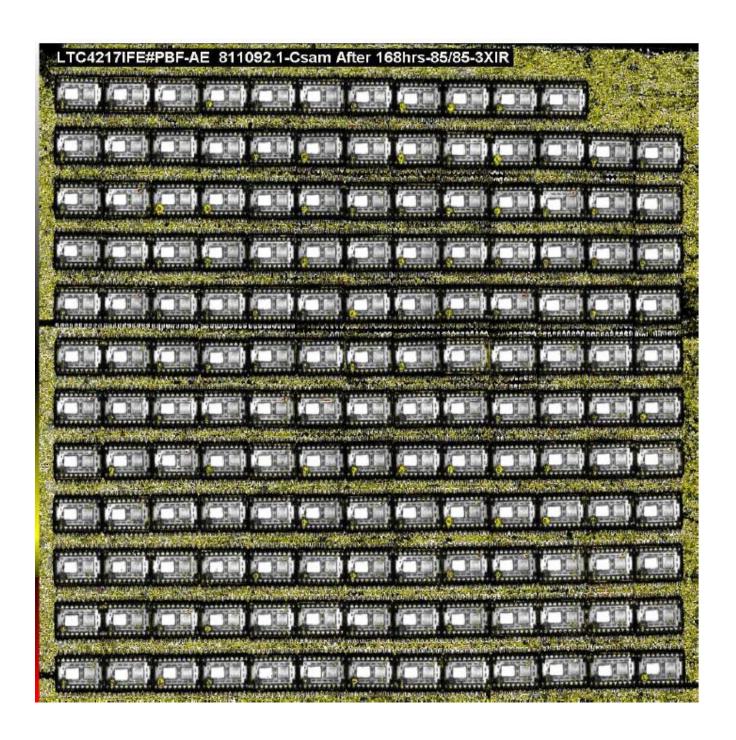

Post MSL 1 Precondition C-SAM image without delamination

### QUALIFICATION DATA LTC4217 Leadframe Change 9/24/2015

| 9/24/2015                                          |                  |                         |                            |                              |                          |  |  |  |  |

|----------------------------------------------------|------------------|-------------------------|----------------------------|------------------------------|--------------------------|--|--|--|--|

| HIGH TEMPERATURE OPERATING LIFE AT 125°C           |                  |                         |                            |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON<br>HTOL           | DEVICE<br>HOURS<br>AT +125°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 78               | 1521                    | 500                        | 39,000                       | 0                        |  |  |  |  |

| <ul> <li>HIGHLY ACCELER</li> </ul>                 | RATED STRESS T   | EST (HAST) AT +13       | 0°C/85% R.H. WITH          | I BIAS <sup>(1)</sup>        |                          |  |  |  |  |

| DEVICE<br>TYPE                                     | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON HAST              | DEVICE<br>HOURS<br>AT +130°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 146              | 1521                    | 96                         | 14,016                       | 0                        |  |  |  |  |

| <ul> <li>PRESSURE COOK</li> </ul>                  | (ER TEST (PCT) A | T 15 PSIG, +121°C/      | /100% R.H <sup>(1,2)</sup> |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON PCT               | DEVICE<br>HOURS<br>AT +130°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 220              | 1521                    | 168.00                     | 36,960                       | 0                        |  |  |  |  |

| TEMP CYCLE FRO                                     | OM -65°C TO +150 | °C <sup>(1,2)</sup>     |                            |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | CYCLES ON TC               | DEVICE<br>HOURS              | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 229              | 1521                    | 1000.00                    | 229,000                      | 0                        |  |  |  |  |

| THERMAL SHOCK                                      | FROM -65°C TO    | +150°C <sup>(1,2)</sup> |                            |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | CYCLES ON<br>TS            | DEVICE<br>HOURS              | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 231              | 1521                    | 1000.00                    | 231,000                      | 0                        |  |  |  |  |

| HIGH TEMPERATU                                     | JRE BAKE AT 150  | °C                      |                            |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON<br>HTB            | DEVICE<br>HOURS<br>AT +125°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 148              | 1521                    | 1,000                      | 148,000                      | 0                        |  |  |  |  |

| <ul> <li>ACCELERATED PI</li> </ul>                 | RECONDITIONING   | 3, 3h PCT + 3x REF      | LOW AT +260°C PE           | AK <sup>(2)</sup>            |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON PCT               | DEVICE<br>HOURS<br>AT +121°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 75               | 1521                    | 3.00                       | 225                          | 0                        |  |  |  |  |

| SOLDER SHOCK, 3h PCT + 1x IMMERSION AT +245°C PEAK |                  |                         |                            |                              |                          |  |  |  |  |

| DEVICE TYPE                                        | SAMPLE<br>SIZE   | DATE CODE               | HOURS ON PCT               | DEVICE<br>HOURS<br>AT +121°C | NUMBER<br>OF<br>FAILURES |  |  |  |  |

| LTC4217                                            | 75               | 1521                    | 3.00                       | 225                          | 0                        |  |  |  |  |

<sup>(1)</sup> Environmental stress are preceded by JEDEC Level 1 Preconditioning: 168h 85°C/85% R.H. plus 3x Reflow at 260°C

<sup>(2)</sup> C-SAM analysis shows superior lamination performance of new leadframe / die attach material compared to control after reflow.

<sup>(3)</sup> Initial electrical test yields at hot are superior for new leadframe / die attach material compared to control.

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}\text{C}$ . $V_{DD} = 12V$ unless otherwise noted.

| SYMBOL                     | PARAMETER                                                        | CONDITIONS                                                                                     |       | MIN        | TYP        | MAX         | UNITS    |

|----------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|------------|------------|-------------|----------|

| Inputs                     |                                                                  | •                                                                                              |       | •          |            |             |          |

| I <sub>IN</sub>            | OV, UV, FB Pin Input Current                                     | V <sub>IN</sub> = 1.2V, LTC4217                                                                | •     |            | 0          | ±1          | μА       |

| R <sub>IN</sub>            | OV, UV, FB Pin Input Resistance                                  | LTC4217-12                                                                                     | •     | 13         | 18         | 23          | kΩ       |

| V <sub>TH</sub>            | OV, UV, FB Pin Threshold Voltage                                 | V <sub>IN</sub> Rising                                                                         | •     | 1.21       | 1.235      | 1.26        | V        |

| ΔV <sub>OV(HYST)</sub>     | OV Pin Hysteresis                                                |                                                                                                | •     | 10         | 20         | 30          | mV       |

| ΔV <sub>UV(HYST)</sub>     | UV Pin Hysteresis                                                |                                                                                                | •     | 50         | 80         | 110         | mV       |

| V <sub>UV(RTH)</sub>       | UV Pin Reset Threshold Voltage                                   | V <sub>UV</sub> Falling                                                                        | •     | 0.55       | 0.62       | 0.7         | V        |

| ΔV <sub>FB(HYST)</sub>     | FB Pin Power Good Hysteresis                                     |                                                                                                | •     | 10         | 20         | 30          | m۷       |

| R <sub>ISET</sub>          | I <sub>SET</sub> Pin Internal Resistor                           |                                                                                                | •     | 19         | 20         | 21          | kΩ       |

| Outputs                    |                                                                  |                                                                                                |       |            |            |             |          |

| V <sub>OL</sub>            | PG, FLT Pin Output Low Voltage                                   | I <sub>OUT</sub> = 2mA<br>C-Grade, I-Grade<br>H-Grade                                          | •     |            | 0.4<br>0.4 | 0.8<br>0.92 | V        |

| I <sub>OH</sub>            | PG, FLT Pin Input Leakage Current                                | V <sub>OUT</sub> = 30V                                                                         | •     |            | 0          | ±10         | μА       |

| V <sub>TIMER(H)</sub>      | TIMER Pin High Threshold                                         | V <sub>TIMER</sub> Rising                                                                      | •     | 1.2        | 1.235      | 1.28        | V        |

| V <sub>TIMER(L)</sub>      | TIMER Pin Low Threshold                                          | V <sub>TIMER</sub> Falling                                                                     | •     | 0.1        | 0.21       | 0.3         | V        |

| I <sub>TIMER(UP)</sub>     | TIMER Pin Pull-Up Current                                        | V <sub>TIMER</sub> = 0V                                                                        | •     | -80        | -100       | -120        | μА       |

| I <sub>TIMER(DN)</sub>     | TIMER Pin Pull-Down Current                                      | V <sub>TIMER</sub> = 1.2V                                                                      | •     | 1.4        | 2          | 2.6         | μА       |

| I <sub>TIMER(RATIO)</sub>  | TIMER Pin Current Ratio ITIMER(DN)/ITIMER(UP)                    |                                                                                                | •     | 1.6        | 2          | 2.7         | %        |

| A <sub>IMON</sub>          | I <sub>MON</sub> Pin Current Gain                                | I <sub>OUT</sub> = 2A                                                                          | •     | 47.5       | 50         | 52.5        | μA/A     |

| I <sub>OFF(IMON)</sub>     | I <sub>MON</sub> Pin Offset Current                              | I <sub>OUT</sub> = 132mA                                                                       | •     | nacd to    | 100        | ±7.5        | μА       |

| I <sub>GATE(UP)</sub>      | Gate Pull-Up Current                                             | Gate Drive On, VGATE = VOUT = 12V                                                              | v cna | -19        | -Z4        | -29         | μА       |

| I <sub>GATE(DN)</sub>      | Gate Pull-Down Current                                           | Gate Drive Off, V <sub>GATE</sub> = 18V, V <sub>OUT</sub> = 12V<br>C-Grade, I-Grade<br>H-Grade | •     | 190<br>164 | 250<br>140 | 400<br>500  | μΑ<br>Αμ |

| I <sub>GATE(FST)</sub>     | Gate Fast Pull-Down Current                                      | Fast Turn Off, V <sub>GATE</sub> = 18V, V <sub>OUT</sub> = 12V                                 |       |            | 140        | 7           | mA       |

| AC Characteri              | stics                                                            |                                                                                                |       | 355uA;     | now        |             |          |

| t <sub>PHL(GATE)</sub>     | Input High (OV), Input Low (UV) to Gate Low<br>Propagation Delay | V <sub>GATE</sub> < 16.5V Falling                                                              | Jed t | o 500uA    | 8          | 10          | μs       |

| t <sub>PHL(ILIM)</sub>     | Short-Circuit to Gate Low                                        | V <sub>FB</sub> = 0, Step I <sub>SENSE</sub> to 1.2A,<br>V <sub>GATE</sub> < 16.5V Falling     | •     |            | 1          | 5           | μs       |

| t <sub>D(ON)</sub>         | Turn-On Delay                                                    | Step V <sub>UV</sub> to 2V, V <sub>GATE</sub> > 13V                                            | •     | 50         | 100        | 150         | ms       |

| t <sub>D(CB)</sub>         | Circuit Breaker Filter Delay Time (Internal)                     | V <sub>FB</sub> = 0V, Step I <sub>SENSE</sub> to 1.2A<br>C-Grade, I-Grade<br>H-Grade           | •     | 1.5<br>1.4 | 2 2        | 2.7<br>2.7  | ms<br>ms |

| t <sub>D(AUTO-RETRY)</sub> | Auto-Retry Turn-On Delay (Internal)                              |                                                                                                | •     | 50         | 100        | 150         | ms       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All currents into pins are positive, all voltages are referenced to GND unless otherwise specified.

Note 3: An internal clamp limits the GATE pin to a maximum of 6.5V above OUT. Driving this pin to voltages beyond the clamp may damage the device.

Note 4: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction

temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 5:**  $T_J$  is calculated from the ambient temperature,  $T_A$ , and power dissipation,  $P_D$ , according to the formula:

LTC4217DHC, LTC4217DHC-12:  $T_J = T_A + (P_D \cdot 43^{\circ}C/W)$ LTC4217FE:  $T_J = T_A + (P_D \cdot 38^{\circ}C/W)$

4217ff

4

For more information www.lineaccom/LTC4217