# Integrated Relay, Inductive Load Driver

## **MDC3105**

This device is intended to replace an array of three to six discrete components with an integrated SMT part. It is available in a SOT-23 package. It can be used to switch 3 to 6 Vdc inductive loads such as relays, solenoids, incandescent lamps, and small DC motors without the need of a free-wheeling diode.

#### **Features**

- Provides a Robust Driver Interface between DC Relay Coil and Sensitive Logic Circuits

- Optimized to Switch Relays from a 3.0 V to 5.0 V Rail

- Capable of Driving Relay Coils Rated up to 2.5 W at 5.0 V

- Features Low Input Drive Current and Good Back-to-Front Transient Isolation

- Internal Zener Eliminates Need for Free-Wheeling Diode

- Internal Zener Clamp Routes Induced Current to Ground for Quieter System Operation

- Guaranteed Off State with No Input Connection

- Supports Large Systems with Minimal Off-State Leakage

- ESD Resistant in Accordance with the Class 1C Human Body Model

- Low Sat Voltage Reduces System Current Drain by Allowing Use of Higher Resistance Relay Coils

- These Devices are Pb-Free and Halide Free

#### **Applications**

- Telecom: Line Cards, Modems, Answering Machines, FAX Machines, Feature Phone Electronic Hook Switch

- Computer and Office: Photocopiers, Printers, Desktop Computers

- Consumer: TVs and VCRs, Stereo Receivers, CD Players, Cassette Recorders, TV Set Top Boxes

- Industrial: Small Appliances, White Goods, Security Systems, Automated Test Equipment, Garage Door Openers

- Automotive: 5.0 V Driven Relays, Motor Controls, Power Latches, Lamp Drivers

## Relay, Inductive Load Driver

#### **MARKING DIAGRAMS**

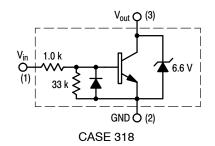

SOT-23 CASE 318 STYLE 6

SC-74 CASE 318F STYLE 8

JW = Specific Device Code

M = Date Code\*

= Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation and/or overbar may vary depending upon manufacturing location.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

## **INTERNAL CIRCUIT DIAGRAMS**

## **MAXIMUM RATINGS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

| Rating                                                   |        | Symbol               | Value       | Unit |

|----------------------------------------------------------|--------|----------------------|-------------|------|

| Power Supply Voltage                                     |        | V <sub>CC</sub>      | 6.0         | Vdc  |

| Input Voltage                                            |        | $V_{in(fwd)}$        | 6.0         | Vdc  |

| Reverse Input Voltage                                    |        | V <sub>in(rev)</sub> | -0.5        | Vdc  |

| Repetitive Pulse Zener Energy Limit (Duty Cycle ≤ 0.01%) | SOT-23 | Ezpk                 | 50          | mJ   |

| Output Sink Current - Continuous                         |        | I <sub>O</sub>       | 500         | mA   |

| Junction Temperature                                     |        | TJ                   | 150         | °C   |

| Operating Ambient Temperature Range                      |        | T <sub>A</sub>       | -40 to +85  | °C   |

| Storage Temperature Range                                |        | T <sub>stg</sub>     | -65 to +150 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### THERMAL CHARACTERISTICS

| Rating                                                       |                 | Symbol         | Value      | Unit        |

|--------------------------------------------------------------|-----------------|----------------|------------|-------------|

| Total Device Power Dissipation (Note 1)<br>Derate above 25°C | SOT-23          | P <sub>D</sub> | 225<br>1.8 | mW<br>mW/°C |

| Total Device Power Dissipation (Note 1)<br>Derate above 25°C | SC-74           | P <sub>D</sub> | 380<br>1.5 | mW<br>mW/°C |

| Thermal Resistance Junction-to-Ambient                       | SOT-23<br>SC-74 | $R_{\thetaJA}$ | 556<br>329 | °C/W        |

<sup>1.</sup> FR-5 PCB of 1" x 0.75" x 0.062",  $T_A = 25$ °C.

## **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                                   | Symbol                                        | Min      | Тур         | Max       | Unit   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------|-------------|-----------|--------|

| OFF CHARACTERISTICS                                                                                                                                              |                                               |          |             |           |        |

| Output Zener Breakdown Voltage<br>(@ IT = 10 mA Pulse)                                                                                                           | V <sub>(BRout)</sub><br>V <sub>(-BRout)</sub> | 6.2<br>– | 6.6<br>-0.7 | 7.0<br>-  | V<br>V |

| Output Leakage Current @ 0 Input Voltage $(V_O = 5.5 \text{ Vdc}, V_{in} = 0.C., T_A = 25^{\circ}C)$ $(V_O = 5.5 \text{ Vdc}, V_{in} = 0.C., T_A = 85^{\circ}C)$ | loo                                           | -<br>-   | -<br>-      | 0.1<br>30 | μΑ     |

| Guaranteed "OFF" State Input Voltage ( $I_O \le 100 \mu A$ )                                                                                                     | V <sub>in(off)</sub>                          | -        | -           | 0.4       | V      |

| ON CHARACTERISTICS                                                                                                                                               |                                               |          |             |           |        |

| Input Bias Current (H <sub>FE</sub> Limited)<br>(I <sub>O</sub> = 250 mA, V <sub>O</sub> = 0.25 Vdc)                                                             | I <sub>in</sub>                               | _        | 0.8         | 1.6       | mAdc   |

| Output Saturation Voltage<br>(I <sub>O</sub> = 250 mA, I <sub>in</sub> = 1.5 mA)                                                                                 | V <sub>O(sat)</sub>                           | -        | 0.12        | 0.16      | Vdc    |

| Output Sink Current - Continuous<br>(V <sub>CE</sub> = 0.25 Vdc, I <sub>in</sub> = 1.5 mA)                                                                       | I <sub>O(on)</sub>                            | 250      | 400         | -         | mA     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## TYPICAL APPLICATION-DEPENDENT SWITCHING PERFORMANCE

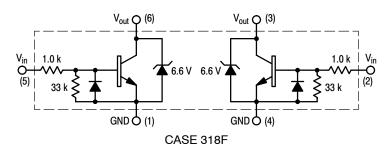

## **SWITCHING CHARACTERISTICS**

| Characteristic                                              | Symbol           | Min | Тур | Max | Units |

|-------------------------------------------------------------|------------------|-----|-----|-----|-------|

| Propagation Delay Times:                                    |                  |     |     |     | nS    |

| High to Low Propagation Delay; Figure 1 (5.0 V 74HC04)      | $t_PHL$          | -   | 55  | -   |       |

| Low to High Propagation Delay; Figure 1 (5.0 V 74HC04)      | t <sub>PLH</sub> | _   | 430 | -   |       |

| High to Low Propagation Delay; Figures 1, 13 (3.0 V 74HC04) | t <sub>PHL</sub> | _   | 85  | _   |       |

| Low to High Propagation Delay; Figures 1, 13 (3.0 V 74HC04) | t <sub>PLH</sub> | _   | 315 | -   |       |

| High to Low Propagation Delay; Figures 1, 14 (5.0 V 74LS04) | t <sub>PHL</sub> | _   | 55  | _   |       |

| Low to High Propagation Delay; Figures 1, 14 (5.0 V 74LS04) | t <sub>PLH</sub> | _   | 2.4 | -   | μS    |

| Transition Times:                                           |                  |     |     |     | nS    |

| Fall Time; Figure 1 (5.0 V 74HC04)                          | t <sub>f</sub>   | _   | 45  | -   |       |

| Rise Time; Figure 1 (5.0 V 74HC04)                          | t <sub>r</sub>   | _   | 160 | -   |       |

| Fall Time; Figures 1, 13 (3.0 V 74HC04)                     | t <sub>f</sub>   | _   | 70  | _   |       |

| Rise Time; Figures 1, 13 (3.0 V 74HC04)                     | t <sub>r</sub>   | _   | 195 | -   |       |

| Fall Time; Figures 1, 14 (5.0 V 74LS04)                     | t <sub>f</sub>   | _   | 45  | _   |       |

| Rise Time; Figures 1, 14 (5.0 V 74LS04)                     | t <sub>r</sub>   | _   | 2.4 | -   | μS    |

Figure 1. Switching Waveforms

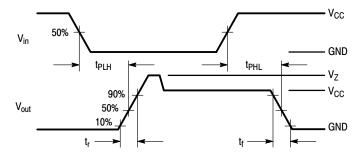

#### TYPICAL PERFORMANCE CHARACTERISTICS

(ON CHARACTERISTICS)

Figure 2. Transistor DC Current Gain

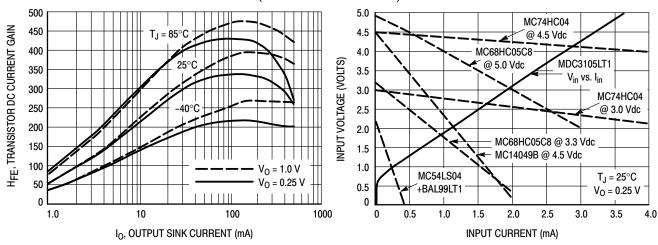

Figure 3. Input V-I Requirement Compared to **Possible Source Logic Outputs**

$T_J = 25^{\circ}C$

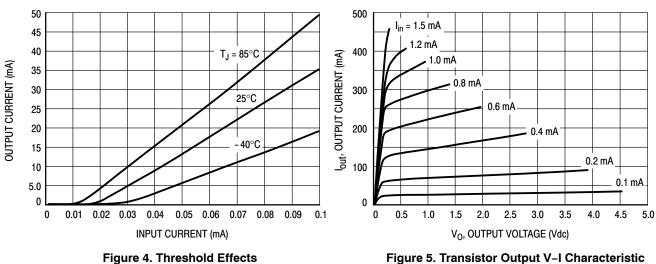

Figure 4. Threshold Effects

1.2 1.1

1.0 0.9 0.8

0.7 0.6 0.5

0.4

0.3 0.2

0.1

0.04

10 mA

0.1

V<sub>out</sub>, OUTPUT VOLTAGE (Vdc)

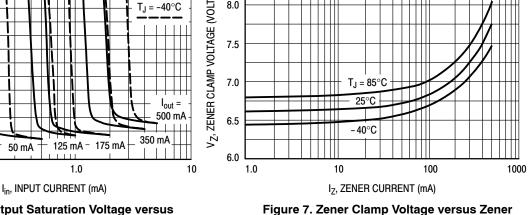

8.5 ZENER CLAMP VOLTAGE (VOLTS) 8.0 7.5 7.0  $T_J = 85^{\circ}C$ 25°C 6.5 -40°C ζ̈́ 6.0 1.0 100

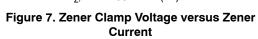

Figure 6. Output Saturation Voltage versus Iout/Iin

### TYPICAL PERFORMANCE CHARACTERISTICS

(OFF CHARACTERISTICS)

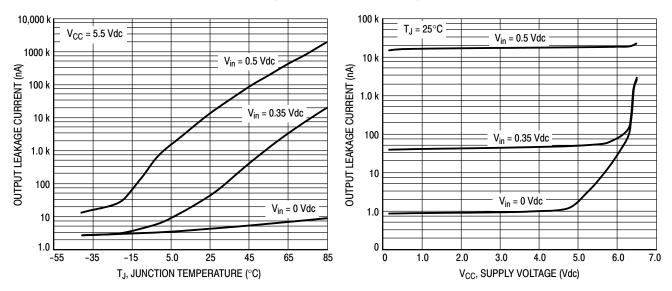

Figure 8. Output Leakage Current versus Temperature

Figure 9. Output Leakage Current versus Supply Voltage

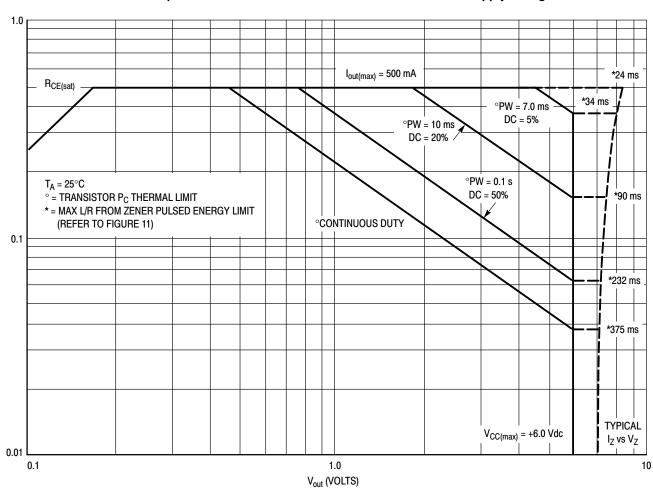

Figure 10. Safe Operating Area for MDC3105LT1

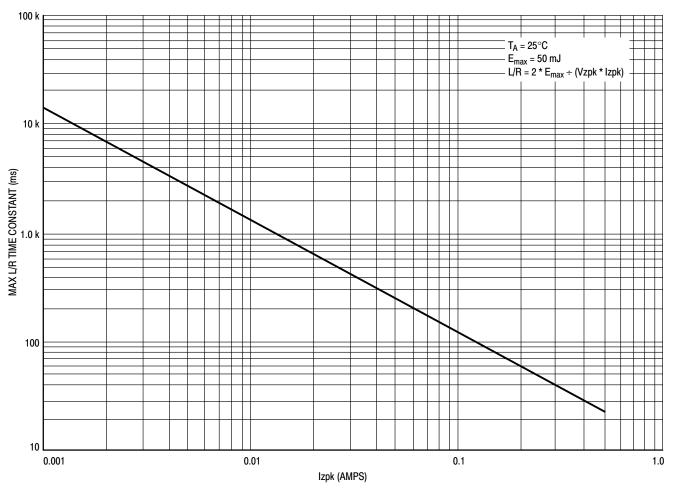

Figure 11. Zener Repetitive Pulse Energy Limit on L/R Time Constant for MDC3105LT1

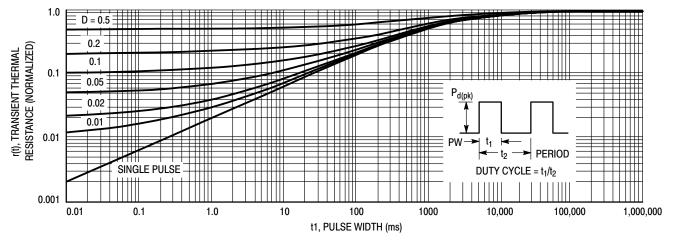

Figure 12. Transient Thermal Response for MDC3105LT1

## **Using TTR Designing for Pulsed Operation**

For a repetitive pulse operating condition, time averaging allows one to increase a device's peak power dissipation rating above the average rating by dividing by the duty cycle of the repetitive pulse train. Thus, a continuous rating of 200 mW of dissipation is increased to 1.0 W peak for a 20% duty cycle pulse train. However, this only holds true for pulse widths which are short compared to the thermal time

constant of the semiconductor device to which they are applied.

For pulse widths which are significant compared to the thermal time constant of the device, the peak operating condition begins to look more like a continuous duty operating condition over the time duration of the pulse. In these cases, the peak power dissipation rating cannot be merely time averaged by dividing the continuous power rating by the duty cycle of the pulse train. Instead, the average power rating can only be scaled up a reduced amount in accordance with the device's transient thermal response, so that the device's max junction temperature is not exceeded.

Figure 12 of the MDC3105 data sheet plots its transient thermal resistance, r(t) as a function of pulse width in ms for various pulse train duty cycles as well as for a single pulse and illustrates this effect. For short pulse widths near the left side of the chart, r(t), the factor, by which the continuous duty thermal resistance is multiplied to determine how much the peak power rating can be increased above the average power rating, approaches the duty cycle of the pulse train, which is the expected value. However, as the pulse width is increased, that factor eventually approaches 1.0 for all duty cycles indicating that the pulse width is sufficiently long to appear as a continuous duty condition to this device. For the MDC3105LT1, this pulse width is about 100 seconds. At this and larger pulse widths, the peak power dissipation capability is the same as the continuous duty power capability.

To use Figure 12 to determine the peak power rating for a specific application, enter the chart with the worst case pulse condition, that is the max pulse width and max duty cycle and determine the worst case r(t) for your application. Then calculate the peak power dissipation allowed by using the equation,

$$Pd(pk) = (T_{Jmax} - T_{Amax}) \div (R_{\theta JA} * r(t))$$

$$Pd(pk) = (150^{\circ}C - T_{Amax}) \div (556^{\circ}C/W * r(t))$$

Thus for a 20% duty cycle and a PW = 40 ms, Figure 12 yields r(t) = 0.3 and when entered in the above equation, the max allowable Pd(pk) = 390 mW for a max  $T_A = 85$ °C.

Also note that these calculations assume a rectangular pulse shape for which the rise and fall times are insignificant compared to the pulse width. If this is not the case in a specific application, then the  $V_O$  and  $I_O$  waveforms should be multiplied together and the resulting power waveform integrated to find the total dissipation across the device. This then would be the number that has to be less than or equal to the Pd(pk) calculated above. A circuit simulator having a waveform calculator may prove very useful for this purpose.

#### **Notes on SOA and Time Constant Limitations**

Figure 10 is the Safe Operating Area (SOA) for the MDC3105. Device instantaneous operation should never be pushed beyond these limits. It shows the SOA for the Transistor "ON" condition as well as the SOA for the Zener during the turn-off transient. The max current is limited by the Izpk capability of the Zener as well as the transistor in addition to the max input current through the resistor. It should not be exceeded at any temperature. The BJT power dissipation limits are shown for various pulse widths and duty cycles at an ambient temperature of 25°C. The voltage limit is the max V<sub>CC</sub> that can be applied to the device. When the input to the device is switched off, the BJT "ON" current is instantaneously dumped into the Zener diode where it begins its exponential decay. The Zener clamp voltage is a function of that BJT current level as can be seen by the bowing of the V<sub>Z</sub> versus I<sub>Z</sub> curve at the higher currents. In addition to the Zener's current limit impacting this device's 500 mA max rating, the clamping diode also has a peak energy limit as well. This energy limit was measured using a rectangular pulse and then translated to an exponential equivalent using the 2:1 relationship between the L/R time constant of an exponential pulse and the pulse width of a rectangular pulse having equal energy content. These L/R time constant limits in ms appear along the Vz versus Iz curve for the various values of Iz at which the Pd lines intersect the V<sub>CC</sub> limit. The L/R time constant for a given load should not exceed these limits at their respective currents. Precise L/R limits on Zener energy at intermediate current levels can be obtained from Figure 11.

#### **Designing with this Data Sheet**

- 1. Determine the maximum inductive load current (at  $\max V_{CC}$ , min coil resistance and usually minimum temperature) that the MDC3105 will have to drive and make sure it is less than the max rated current.

- For pulsed operation, use the Transient Thermal Response of Figure 12 and the instructions with it to determine the maximum limit on transistor power dissipation for the desired duty cycle and temperature range.

- 3. Use Figures 10 and 11 with the SOA notes above to insure that instantaneous operation does not push the device beyond the limits of the SOA plot.

- While keeping any V<sub>O(sat)</sub> requirements in mind, determine the max input current needed to achieve that output current from Figures 2 and 6.

- 5. For levels of input current below  $100 \,\mu\text{A}$ , use the input threshold curves of Figure 4 to verify that there will be adequate input current available to turn on the MDC3105 at all temperatures.

- 6. For levels of input current above 100  $\mu$ A, enter Figure 3 using that max input current and determine the input voltage required to drive the MDC3105 from the solid  $V_{in}$  versus  $I_{in}$  line. Select a suitable drive source family from those whose dotted lines

- cross the solid input characteristic line to the right of the  $I_{in}$ ,  $V_{in}$  point.

- 7. Using the max output current calculated in step 1, check Figure 7 to insure that the range of Zener clamp voltage over temperature will satisfy all system and EMI requirements.

- 8. Using Figures 8 and 9, insure that "OFF" state leakage over temperature and voltage extremes does not violate any system requirements.

- 9. Review circuit operation and insure none of the device max ratings are being exceeded.

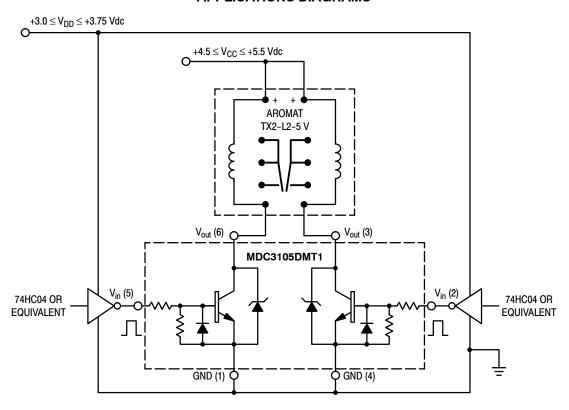

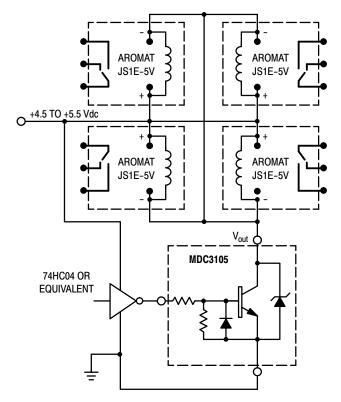

#### **APPLICATIONS DIAGRAMS**

Figure 13. A 200 mW, 5.0 V Dual Coil Latching Relay Application with 3.0 V-HCMOS Level Translating Interface

#### **Max Continuous Current Calculation**

for TX2–5V Relay, R1 = 178  $\Omega$  Nominal @ R<sub>A</sub> = 25°C Assuming  $\pm 10\%$  Make Tolerance, R1 = 178  $\Omega$  \* 0.9 = 160  $\Omega$  Min @ T<sub>A</sub> = 25°C T<sub>C</sub> for Annealed Copper Wire is 0.4%/°C R1 = 160  $\Omega$  \* [1+(0.004) \* (-40°-25°)] = 118  $\Omega$  Min @ -40°C I<sub>O</sub> Max = (5.5 V Max – 0.25V) /118  $\Omega$  = 45 mA

74LS04

BAL99LT1

V<sub>in</sub>

GND Q

Figure 14. A 140 mW, 5.0 V Relay with TTL Interface

Figure 15. A Quad 5.0 V, 360 mW Coil Relay Bank

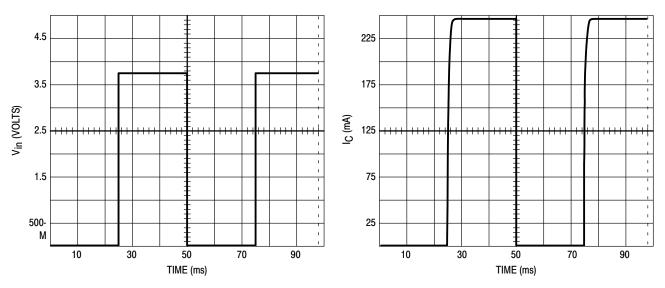

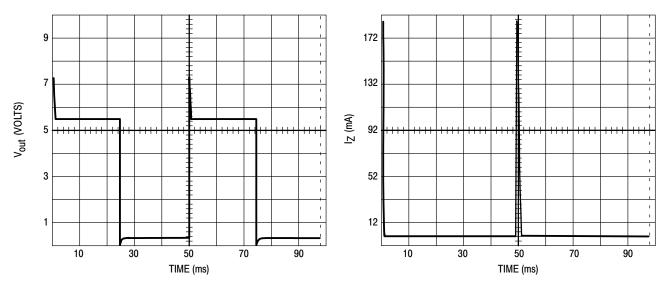

### **TYPICAL OPERATING WAVEFORMS**

Figure 16. 20 Hz Square Wave Input

Figure 17. 20 Hz Square Wave Response

Figure 18. 20 Hz Square Wave Response

MDC3105LT1G

Figure 19. 20 Hz Square Wave Response

## **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| MDC3105LT1G  | SOT-23<br>(Pb-Free) | 3000 / Tape & Reel    |

| MDC3105DMT1G | SC-74<br>(Pb-Free)  | 3000 / Таре и пеет    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

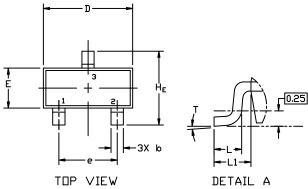

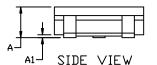

**SOT-23 (TO-236)** CASE 318 ISSUE AT

**DATE 01 MAR 2023**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M,1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF THE BASE MATERIAL.

- 4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.

|     | MILLIMETERS |      |      | INCHES |       |       |

|-----|-------------|------|------|--------|-------|-------|

| DIM | MIN.        | N□M. | MAX. | MIN.   | N□M.  | MAX.  |

| Α   | 0.89        | 1.00 | 1.11 | 0.035  | 0.039 | 0.044 |

| A1  | 0.01        | 0.06 | 0.10 | 0.000  | 0.002 | 0.004 |

| b   | 0.37        | 0.44 | 0.50 | 0.015  | 0.017 | 0.020 |

| С   | 0.08        | 0.14 | 0.20 | 0.003  | 0.006 | 0.008 |

| D   | 2.80        | 2.90 | 3.04 | 0.110  | 0.114 | 0.120 |

| Ε   | 1.20        | 1.30 | 1.40 | 0.047  | 0.051 | 0.055 |

| e   | 1.78        | 1.90 | 2.04 | 0.070  | 0.075 | 0.080 |

| L   | 0.30        | 0.43 | 0.55 | 0.012  | 0.017 | 0.022 |

| L1  | 0.35        | 0.54 | 0.69 | 0.014  | 0.021 | 0.027 |

| HE  | 2.10        | 2.40 | 2.64 | 0.083  | 0.094 | 0.104 |

| Т   | 0*          |      | 10°  | 0*     |       | 10°   |

# GENERIC MARKING DIAGRAM\*

XXX = Specific Device Code

M = Date Code

■ = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

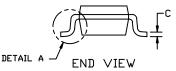

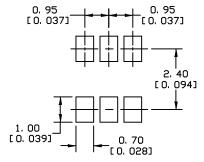

RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42226B     | Electronic versions are uncontrolled except when accessed directly from the Document Reposit Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOT-23 (TO-236) |                                                                                                                                                                              | PAGE 1 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

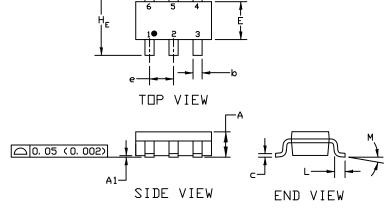

## MECHANICAL CASE OUTLINE PACKAGE DIMENSIONS

### **SOT-23 (TO-236)** CASE 318 ISSUE AT

**DATE 01 MAR 2023**

| STYLE 1 THRU 5:<br>CANCELLED                            | STYLE 6:<br>PIN 1. BASE<br>2. EMITTER<br>3. COLLECTOR | STYLE 7:<br>PIN 1. EMITTER<br>2. BASE<br>3. COLLECTOR       | STYLE 8:<br>PIN 1. ANODE<br>2. NO CONNECTION<br>3. CATHODE  | N                                                             |                                                             |

|---------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| STYLE 9:<br>PIN 1. ANODE<br>2. ANODE<br>3. CATHODE      | STYLE 10:<br>PIN 1. DRAIN<br>2. SOURCE<br>3. GATE     | STYLE 11: PIN 1. ANODE 2. CATHODE 3. CATHODE-ANODE          | STYLE 12: PIN 1. CATHODE 2. CATHODE 3. ANODE                | STYLE 13:<br>PIN 1. SOURCE<br>2. DRAIN<br>3. GATE             | STYLE 14:<br>PIN 1. CATHODE<br>2. GATE<br>3. ANODE          |

| STYLE 15:<br>PIN 1. GATE<br>2. CATHODE<br>3. ANODE      | STYLE 16:<br>PIN 1. ANODE<br>2. CATHODE<br>3. CATHODE | STYLE 17:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. CATHODE | STYLE 18:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. ANODE | STYLE 19:<br>N PIN 1. CATHODE<br>2. ANODE<br>3. CATHODE-ANODE | STYLE 20:<br>PIN 1. CATHODE<br>2. ANODE<br>3. GATE          |

| STYLE 21:<br>PIN 1. GATE<br>2. SOURCE<br>3. DRAIN       | STYLE 22:<br>PIN 1. RETURN<br>2. OUTPUT<br>3. INPUT   | STYLE 23:<br>PIN 1. ANODE<br>2. ANODE<br>3. CATHODE         | STYLE 24:<br>PIN 1. GATE<br>2. DRAIN<br>3. SOURCE           | STYLE 25:<br>PIN 1. ANODE<br>2. CATHODE<br>3. GATE            | STYLE 26:<br>PIN 1. CATHODE<br>2. ANODE<br>3. NO CONNECTION |

| STYLE 27:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE | STYLE 28:<br>PIN 1. ANODE<br>2. ANODE<br>3. ANODE     |                                                             |                                                             |                                                               |                                                             |

| DOCUMENT NUMBER: | 98ASB42226B     | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOT-23 (TO-236) |                                                                                                                                                                                   | PAGE 2 OF 2 |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

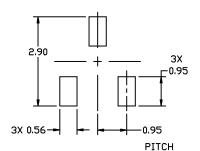

SC-74 CASE 318F ISSUE P

**DATE 07 OCT 2021**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994

- 2. CONTROLLING DIMENSION: INCHES

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF THE BASE MATERIAL.

|                | MILLIMETERS |       |       |        | INCHES |        |

|----------------|-------------|-------|-------|--------|--------|--------|

| DIM            | MIN.        | N□M.  | MAX.  | MIN.   | N□M.   | MAX.   |

| Α              | 0. 90       | 1. 00 | 1. 10 | 0. 035 | 0. 039 | 0. 043 |

| A1             | 0. 01       | 0. 06 | 0. 10 | 0. 001 | 0. 002 | 0. 004 |

| ھ              | 0, 25       | 0. 37 | 0. 50 | 0. 010 | 0. 015 | 0. 020 |

| С              | 0.10        | 0. 18 | 0. 26 | 0. 004 | 0. 007 | 0. 010 |

| D              | 2. 90       | 3. 00 | 3. 10 | 0. 114 | 0. 118 | 0. 122 |

| Ε              | 1. 30       | 1. 50 | 1. 70 | 0. 051 | 0. 059 | 0. 067 |

| е              | 0. 85       | 0. 95 | 1. 05 | 0. 034 | 0. 037 | 0. 041 |

| Η <sub>E</sub> | 2. 50       | 2. 75 | 3. 00 | 0. 099 | 0. 108 | 0. 118 |

| L              | 0. 20       | 0. 40 | 0. 60 | 0. 008 | 0. 016 | 0. 024 |

| М              | 0*          |       | 10*   | 0*     |        | 10*    |

## GENERIC MARKING DIAGRAM\*

XXX = Specific Device Code

M = Date Code ■ = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

For additional information on our Pb-Free strategy and soldering details, please download the UN Seniconductor Soldering and Mounting Techniques Reference Manual, SULDERRM/D.

SOLDERING FOOTPRINT

| STYLE 1:<br>PIN 1. CATHODE<br>2. ANODE<br>3. CATHODE<br>4. CATHODE<br>5. ANODE<br>6. CATHODE     | STYLE 2: PIN 1. NO CONNECTION 2. COLLECTOR 3. EMITTER 4. NO CONNECTION 5. COLLECTOR 6. BASE | STYLE 3: PIN 1. EMITTER 1 2. BASE 1 3. COLLECTOR 2 4. EMITTER 2 5. BASE 2 6. COLLECTOR 1 | STYLE 4: PIN 1. COLLECTOR 2 2. EMITTER 1/EMITTER 2 3. COLLECTOR 1 4. EMITTER 3 5. BASE 1/BASE 2/COLLECTOR 3 6. BASE 3 | STYLE 5:<br>PIN 1. CHANNEL 1<br>2. ANODE<br>3. CHANNEL 2<br>4. CHANNEL 3<br>5. CATHODE<br>6. CHANNEL 4 | STYLE 6:<br>PIN 1. CATHODE<br>2. ANODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. SOURCE 1<br>2. GATE 1<br>3. DRAIN 2<br>4. SOURCE 2<br>5. GATE 2<br>6. DRAIN 1 | STYLE 8: PIN 1. EMITTER 1 2. BASE 2 3. COLLECTOR 2 4. EMITTER 2 5. BASE 1 6. COLLECTOR 1    | STYLE 9: PIN 1. EMITTER 2 2. BASE 2 3. COLLECTOR 1 4. EMITTER 1 5. BASE 1 6. COLLECTOR 2 | STYLE 10: PIN 1. ANODE/CATHODE 2. BASE 3. EMITTER 4. COLLECTOR 5. ANODE 6. CATHODE                                    | STYLE 11: PIN 1. EMITTER 2. BASE 3. ANODE/CATHOD 4. ANODE 5. CATHODE 6. COLLECTOR                      | E                                                                                              |

| DOCUMENT NUMBER: | 98ASB42973B | Electronic versions are uncontrolled except when accessed directly from the Document Repositor,<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SC-74       |                                                                                                                                                                                    | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative