# PWM Controller, Input Current Mode, Ultra Wide

## NCP12700

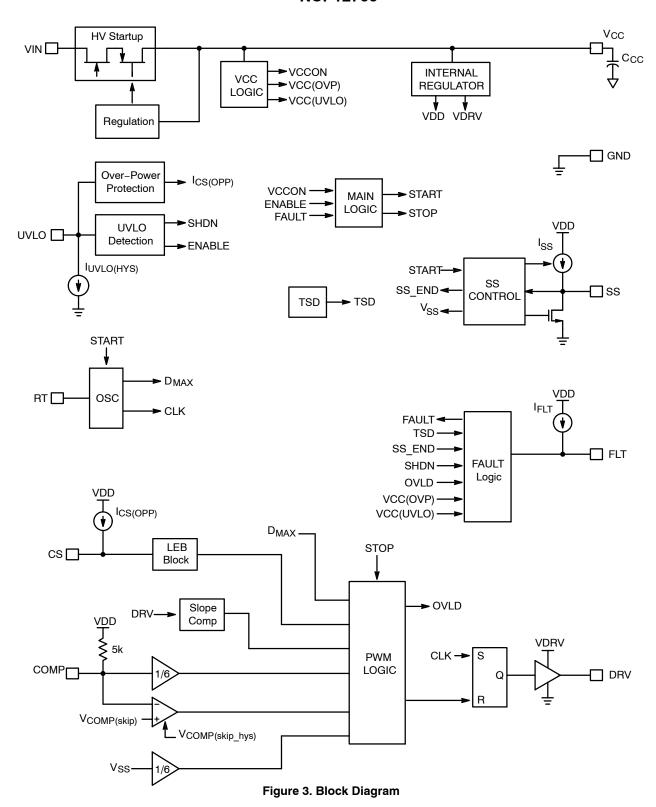

The NCP12700 is a fixed frequency, peak current mode, PWM controller containing all of the features necessary for implementing single–ended power converter topologies. The device features a high voltage startup capable of operating over a wide input range and supplying at least 15 mA to provide temporary bias to  $V_{\rm CC}$  during system startup. The device contains a programmable oscillator capable of operating from 100 kHz to 1 MHz and integrates slope compensation to prevent subharmonic oscillations. The controller offers an adjustable soft–start, input voltage UVLO protection, and an adjustable Over–Power Protection circuit which limits the total power capability of the circuit as the input voltage increases, easing the system thermal design. The UVLO pin also features a shutdown comparator which allows for an external signal to disable switching and bring the controller into a low quiescent state.

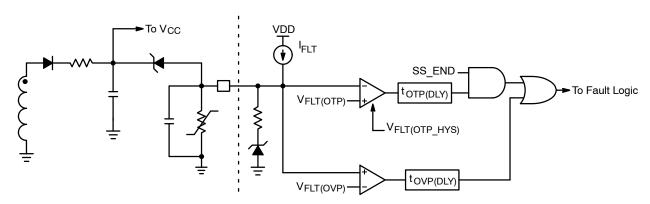

The NCP12700 contains a suite of protection features including cycle-by-cycle peak current limiting, timer-based overload protection, and a FLT pin which can be interfaced with an NTC and an auxiliary winding to provide system thermal protection and output over-voltage protection. All protection features place the device into a low quiescent fault mode and recovery from fault mode is dependent on the device option.

## **Common General Features**

- Wide Input Range (9 120/200 V; MSOP10/WQFN10)

- Startup Regulator Circuit with 15 mA Capability

- Current Mode Control with Integrated Slope Compensation

- Suitable for Flyback or Forward Converters

- Single Resistor Programmable Oscillator

- 1 A / 2.8 A Source / Sink Gate Driver

- User Adjustable Soft-Start Ramp

- Input Voltage UVLO with Hysteresis

- Shutdown Threshold for External Disable

- Skip Cycle Mode for Low Standby Power

- This is a Pb-Free Device

## **Fault Protection Features**

- User Adjustable Over-Power Protection

- Overload Protection with 30 ms Overload Timer

- NTC-Compatible Fault Interface for Thermal Protection

- Output OVP Fault Interface

- Fault Auto-recovery Mode with 1 s Auto-recovery Period

## ON Semiconductor®

www.onsemi.com

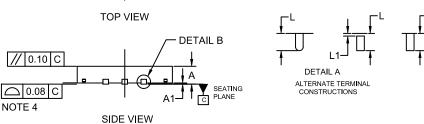

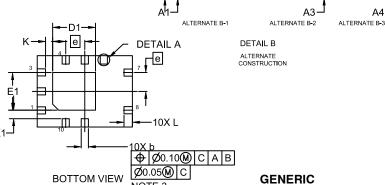

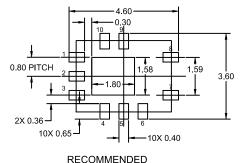

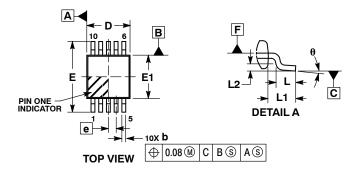

WQFN10 MT SUFFIX CASE 511DV

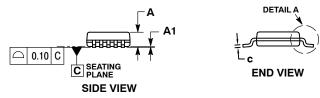

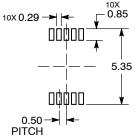

MSOP DN SUFFIX CASE 846AE

#### **MARKING DIAGRAMS**

12700 or 700 = Specific Device Code

x = A, B or C

A = Assembly Site

L = Wafer Lot Number

YW = Assembly Start Week

Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.

## **Typical Applications**

1

- Single-ended Power Converters including CCM/DCM Flyback and Forward Converters

- Telecommunications Power Converters

- Industrial Power Converter Modules

- Transportation & Railway Power Modules

- Power over Ethernet Powered Devices (PoE PD)

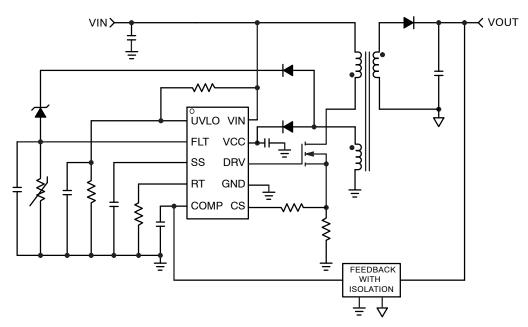

Figure 1. Typical Application Circuit for Vin = 12 - 160 V

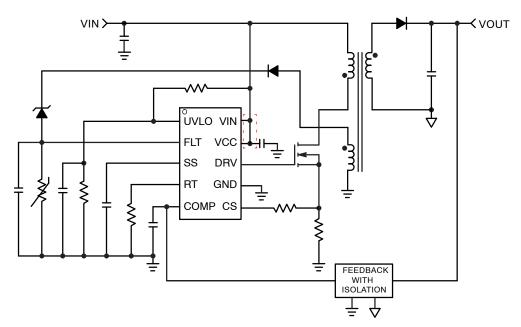

Figure 2. Typical Application Circuit for Vin = 9 - 18 V

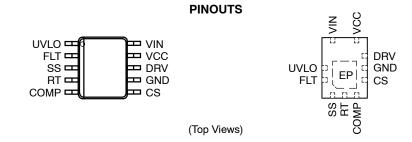

**Table 1. PIN FUNCTION DESCRIPTION**

| MSOP10 | WQFN10 | Pin Name | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | 9      | UVLO     | The UVLO pin is the input to the Standby and UVLO comparators. A resistor divider between the power supply input voltage and ground is connected to the UVLO pin to set the input voltage level at which the controller will be enabled. UVLO Hysteresis is set by a 5 $\mu$ A pull–down current source. An externally supplied pull–down signal can also be used to disable the controller. The UVLO pin is also used to determine the Over–Power Protection current supplied to the CS pin.                                              |

| 2      | 10     | FLT      | The FLT pin is the input to a window comparator which provides an upper and lower fault threshold. When either threshold is tripped, the controller enters the fault mode which can be a permanent latch off or a minimum 1 s auto-recovery period. A precision current source is output from the FLT pin allowing an NTC to ground to be placed at the pin for system Over-temperature protection. The upper threshold can be used for output over-voltage protection sensed through the auxiliary winding or as a general purpose fault. |

| 3      | 1      | SS       | The SS pin sets the soft–start ramp of the peak current limit when the controller is enabled. An internal 15 $\mu$ A current source and an external capacitor to ground are used to control the ramp rate. Typical soft start capacitor values will be in the range of 10 nF to 100 nF.                                                                                                                                                                                                                                                    |

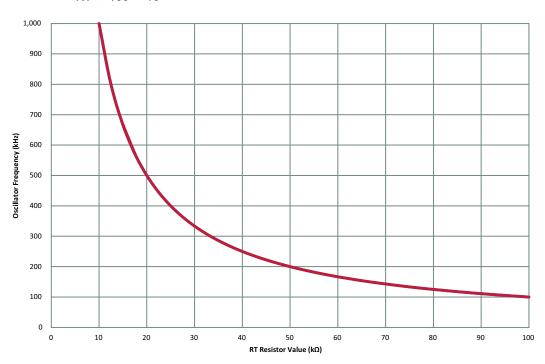

| 4      | 2      | RT       | The RT pin sets the oscillator frequency in the controller. This pin requires a resistor to ground located close to the IC. Typical RT values are in the range of 10 k $\Omega$ – 100 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                         |

| 5      | 3      | COMP     | The COMP pin provides the compensated error voltage for the PWM and Skip comparators. An internal 5 k $\Omega$ pull-up resistor is connected to the COMP pin and can be used to bias the transistor of an opto-coupler.                                                                                                                                                                                                                                                                                                                    |

| 6      | 4      | CS       | The CS pin is the current sense input for the PWM and Current Limit comparators. The comparator input is held low for 60 ns after the DRV goes high to prevent leading edge current spikes from tripping the comparators. An external low pass filter is recommended for improved noise immunity. The external filter resistor is also used to determine the amount of Over–Power Protection applied to the current sense.                                                                                                                 |

| 7      | 5      | GND      | This pin is the controller ground. For the WQFN package the exposed pad (EP) should be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8      | 6      | DRV      | The DRV pin is a high current output used to drive the external MOSFET gate. DRV has source and sink capability of 1 A and 2.8 A, respectively.                                                                                                                                                                                                                                                                                                                                                                                            |

| 9      | 7      | VCC      | The VCC pin provides bias to the controller. An external decoupling capacitor to ground in the range of 1 $-$ 10 $\mu F$ is recommended.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10     | 8      | VIN      | The VIN pin is the input to the high voltage startup regulator. The regulator is capable of sourcing > 15 mA to temporarily bias VCC while the application is starting up.                                                                                                                                                                                                                                                                                                                                                                 |

## **ORDERING INFORMATION**

| OHDEHING IN OHIM                   |         |                      |              |              |                       |

|------------------------------------|---------|----------------------|--------------|--------------|-----------------------|

| Device                             | Package | V <sub>CS(LIM)</sub> | OTP Fault    | OVP Fault    | Shipping <sup>†</sup> |

| NCP12700ADNR2G                     | MSOP10  | 495 mV               | Latch        | Latch        | 4000 / Tape & Reel    |

| NCP12700BDNR2G                     | MSOP10  | 495 mV               | Autorecovery | Autorecovery | 4000 / Tape & Reel    |

| NCP12700CDNR2G<br>(In Development) | MSOP10  | 250 mV               | Autorecovery | Autorecovery | 4000 / Tape & Reel    |

| NCP12700BMTTXG                     | WQFN10  | 495 mV               | Autorecovery | Autorecovery | 3000 / Tape & Reel    |

| NCP12700CMTTXG<br>(In Development) | WQFN10  | 250 mV               | Autorecovery | Autorecovery | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | Symbol                | Value                            | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|----------------------------------|------|

| High Voltage Startup Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (MSOP10)<br>(WQFN10) | $V_{IN(MAX)}$         | 120<br>200                       | V    |

| High Voltage Startup Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | I <sub>IN(MAX)</sub>  | 50                               | mA   |

| Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | V <sub>CC(MAX)</sub>  | -0.3 to 30                       | V    |

| Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | I <sub>CC(MAX)</sub>  | 50                               | mA   |

| DRV Voltage (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | V <sub>DRV(MAX)</sub> | −0.3 V to V <sub>DRV(high)</sub> | V    |

| DRV Current (Peak)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | I <sub>DRV(MAX)</sub> | 3.25                             | Α    |

| FLT Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | V <sub>FLT(MAX)</sub> | V <sub>CC</sub> + 1.25           | V    |

| FLT Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | I <sub>FLT(MAX)</sub> | 10                               | mA   |

| Max Voltage on Signal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | V <sub>SIG(MAX)</sub> | -0.3 to 5.5                      | V    |

| Max Current on Signal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | I <sub>SIG(MAX)</sub> | 10                               | mA   |

| Thermal Resistance Junction-to-Air (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (MSOP10)<br>(WQFN10) | $R_{\thetaJ-A}$       | 165<br>51                        | °C/W |

| Junction-to-Top Thermal Characterization Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (MSOP10)<br>(WQFN10) | $\Psi_{J-C}$          | 10<br>12                         | °C/W |

| Maximum Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | T <sub>JMAX</sub>     | 150                              | °C   |

| Maximum Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (MSOP10)<br>(WQFN10) | $P_{D}$               | Internally Limited               | W    |

| Storage Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      | T <sub>STG</sub>      | -55 to 150                       | °C   |

| Operating Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | TJ                    | -40 to 125                       | °C   |

| ESD Capability (Note 3)  Human Body Model per JEDEC Standard of Charge Device D |                      |                       | 2000<br>1000                     | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 3. This device series contains ESD protection and exceeds the following tests: Human Body Model 2000 V per JEDEC Standard JESD22-A114E Charge Device Model TBD per JEDEC Standard JESD22-C101E

- 4. This device contains latch-up protection and has been tested per JEDEC JESD78D, Class I and exceeds +/-100 mA (TBD).

### **Table 3. RECOMMENDED OPERATING CONDITIONS**

| Rating                      |                      | Symbol          | Value               | Unit |

|-----------------------------|----------------------|-----------------|---------------------|------|

| VIN Voltage                 | (MSOP10)<br>(WQFN10) | V <sub>IN</sub> | 9 – 100<br>12 – 160 | V    |

| Supply Voltage – All        |                      | V <sub>CC</sub> | 9 – 20 V            | V    |

| Operating Temperature Range |                      | TJ              | -40 to 125          | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Maximum driver voltage is limited by the driver clamp voltage, V<sub>DRV(high)</sub>, when V<sub>CC</sub> exceeds the driver clamp voltage. Otherwise, the maximum driver voltage is V<sub>CC</sub>.

2. Per JEDEC specification JESD51.7 using two 1 oz copper planes with board size = 80x80x1.6 mm

| Characteristics                                           | Test Condition                                                                          | Symbol                                      | Min                    | Тур          | Max                    | Uni                      |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|------------------------|--------------|------------------------|--------------------------|

| HIGH VOLTAGE STARTUP REGULATO                             | )R                                                                                      | •                                           | •                      |              | •                      | •                        |

| Regulated Voltage                                         | V <sub>CC</sub> = Open, I <sub>CC</sub> = 5 mA                                          | V <sub>CC(REG)</sub>                        | 7.6                    | 8            | 8.4                    | V                        |

| Current Source Capability                                 | V <sub>IN</sub> = 9 V, V <sub>CC</sub> = 7 V                                            | I <sub>VIN(SRC)</sub>                       | 15                     |              |                        | mA                       |

| Current Source Limit                                      | V <sub>CC</sub> = V <sub>CC(off)</sub> + 100 mV                                         | I <sub>VIN(LIM)</sub>                       |                        | 30           |                        | mA                       |

| Off-State Leakage Current (xMTTXG)                        | V <sub>CC</sub> = Open, V <sub>IN</sub> = 160 V, V <sub>UVLO</sub> = 0                  | I <sub>VIN(OFF)</sub>                       |                        |              | 100                    | μА                       |

| Off-State Leakage Current (xDNR2G)                        | V <sub>CC</sub> = Open, V <sub>IN</sub> = 120 V, V <sub>UVLO</sub> = 0                  | I <sub>VIN(OFF)</sub>                       |                        |              | 100                    | μΑ                       |

| SUPPLY CIRCUIT                                            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                 | *(0)                                        | ı                      | <u> </u>     | <u>l</u>               |                          |

| Supply Voltage                                            | 1                                                                                       |                                             |                        |              |                        | V                        |

| Startup Threshold                                         | V <sub>CC</sub> increasing                                                              | V <sub>CC(on)</sub>                         | V <sub>CC(REG)</sub> - |              | V <sub>CC(REG)</sub> – |                          |

| Minimum Operating Voltage                                 | V <sub>CC</sub> decreasing                                                              | Voor m                                      | 35Ò mÝ<br>6.2          | 6.5          | 10Ò mỨ<br>6.8          |                          |

|                                                           | vec decreasing                                                                          | V <sub>CC(off)</sub>                        | 0.2                    |              | 0.0                    | V                        |

| Supply Over-Voltage Protection                            |                                                                                         | V <sub>CC(OVP)</sub>                        |                        | 28           |                        |                          |

| VCC OVP Detection Filter Delay                            |                                                                                         | tvccovp<br>(DLY)                            |                        | 3            |                        | μS                       |

| Startup Delay                                             | Measured from $V_{CC(ON)}$ to SS                                                        | t <sub>ON(Dly)</sub>                        |                        |              | 25                     | μs                       |

| Supply Current SHDN STBY                                  | V <sub>UVLO</sub> = 0 V<br>V <sub>UVLO</sub> = 0.7 V                                    | I <sub>CC(SHDN)</sub> I <sub>CC(STBY)</sub> | -<br>-                 |              | 50<br>750              | μ <b>Α</b><br>μ <b>Α</b> |

| Enable<br>Fault                                           | $C_{DRV}$ = Open, $V_{COMP}$ = 2 V<br>$V_{FLT}$ = 0 V                                   | I <sub>CC(EN)</sub>                         | _                      | _            | 4<br>500               | mA<br>μA                 |

| CURRENT SENSE                                             | VFLI - 5 V                                                                              | ICC(FLT)                                    |                        |              | 300                    | μ                        |

|                                                           | NCD10700CDND0C                                                                          | Lv                                          | 005                    | 050          | 065                    | \                        |

| Current Limit Comparator Threshold                        | NCP12700CDNR2G<br>Other parts                                                           | V <sub>CS(LIM)</sub>                        | 235<br>465             | 250<br>495   | 265<br>525             | m√                       |

| Propagation Delay From Current<br>Sense Limit to DRV Low  | Step V <sub>CS</sub> from 0 – 0.6 V                                                     | t <sub>CS(DLY)</sub>                        | _                      | -            | 75                     | ns                       |

| Short Circuit Protection (SCP) Current<br>Limit Threshold | NCP12700CDNR2G<br>Other parts                                                           | V <sub>SCP(LIM)</sub>                       |                        | 312.5<br>625 |                        | mV                       |

| Propagation Delay From Short Circuit<br>Limit to DRV Low  | V <sub>CS</sub> = 0.75 V                                                                | t <sub>SCP(DLY)</sub>                       | -                      | -            | 75                     | ns                       |

| Short Circuit Counter                                     | V <sub>CS</sub> = 0.75 V                                                                | N <sub>SCP</sub>                            |                        | 4            |                        |                          |

| CS Leading Edge Blanking (LEB)                            |                                                                                         | t <sub>LEB(CS)</sub>                        | 75                     | 100          | 125                    | ns                       |

| SCP Leading Edge Blanking                                 |                                                                                         | t <sub>LEB(SCP)</sub>                       | 45                     | 60           | 75                     | ns                       |

| CS LEB Pull-down Resistance                               |                                                                                         | R <sub>PD(LEB)</sub>                        |                        | -            | 55                     | Ω                        |

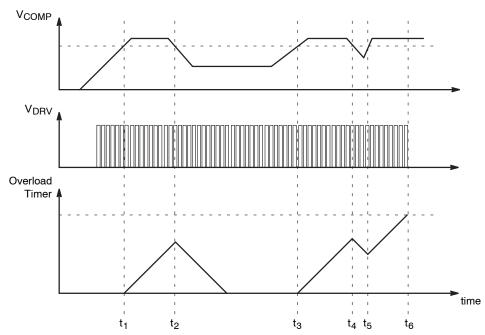

| Overload Timer Duration                                   | V <sub>CS</sub> = 0.6 V                                                                 | t <sub>CS(OVLD)</sub>                       | 24                     | 30           | 36                     | ms                       |

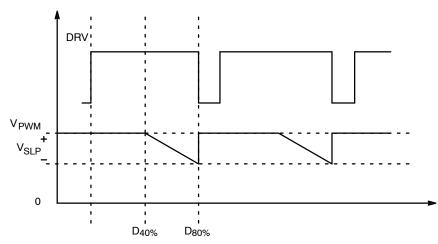

| Applied Slope Compensation @ Current Limit Comparator     | V <sub>COMP</sub> = Open; Measured at D <sub>80%</sub><br>NCP12700CDNR2G<br>Other parts | V <sub>SLP(ILIM)</sub>                      | 35<br>83               | 50<br>102    | 65<br>123              | m۱                       |

| Duty Cycle Where Slope Compensating Ramp Begins           |                                                                                         | D <sub>40%</sub>                            |                        | 40           |                        | %                        |

| COMP SECTION                                              | •                                                                                       | •                                           | •                      |              | •                      |                          |

| PWM to COMP Gain Through Resistor<br>Divider              | V <sub>COMP</sub> = 2 V                                                                 | K <sub>PWM</sub>                            |                        | 6            |                        |                          |

| PWM Propagation Delay to DRV Low                          | V <sub>COMP</sub> = 2 V, Step from CS 0– 0.4 V                                          | t <sub>PWM(Dly)</sub>                       |                        | -            | 75                     | ns                       |

| COMP Open Pin Voltage                                     |                                                                                         | V <sub>COMP(open)</sub>                     | 4                      | 4.7          |                        | ٧                        |

| COMP Output Current                                       | V <sub>COMP</sub> = 0                                                                   | I <sub>COMP</sub>                           | 0.84                   | 1            | 1.2                    | m <i>P</i>               |

| Maximum Duty Cycle                                        | V <sub>COMP</sub> = Open                                                                | D <sub>MAX</sub>                            | 76                     | 80           | 84                     | %                        |

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ (V_{IN} = 12 \ \text{V}, \ V_{CC} = 12 \ \text{V}, \ V_{COMP} = \text{Open}, \ V_{FLT} = \text{Open}, \ C_{DRV} = 1 \ \text{nF}, \ R_T = 49.9 \text{k}, \ V_{CS} = 0 \ \text{V}, \ V_{SS} = \text{Open}, \ V_{UVLO} = 1.2, \ \text{for typical values} \ T_J = 25^{\circ}\text{C}, \ \text{for min/max values}, \ T_J \ \text{is} - \textbf{40}^{\circ}\text{C} \ \text{to} \ \textbf{125}^{\circ}\text{C}, \ \text{unless otherwise noted})$

| Characteristics                                      | Test Condition                                                                         | Symbol                       | Min      | Тур      | Max       | Unit           |

|------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|----------|----------|-----------|----------------|

| COMP SECTION                                         |                                                                                        |                              |          |          |           |                |

| COMP Skip Threshold                                  |                                                                                        | V <sub>COMP(skip)</sub>      |          | 300      |           | mV             |

| COMP Skip Hysteresis                                 |                                                                                        | V <sub>COMP</sub> (skip_hys) |          | 25       |           | mV             |

| Minimum Duty Cycle                                   | V <sub>COMP</sub> = 0                                                                  | D <sub>MIN</sub>             |          |          | 0         | %              |

| Applied Slope Compensation @ PWM Comparator          | V <sub>COMP</sub> = 2 V; Measured at D <sub>80%</sub><br>NCP12700CDNR2G<br>Other parts | V <sub>SLP(PWM)</sub>        | 30<br>77 | 40<br>98 | 50<br>117 | mV             |

| SOFT START                                           |                                                                                        |                              |          |          |           |                |

| Soft-Start Open Pin Voltage                          |                                                                                        | V <sub>SS(open)</sub>        |          | 5.0      |           | V              |

| Soft-Start End Threshold                             |                                                                                        | V <sub>SS(end)</sub>         | 2.85     | 3        | 3.15      | V              |

| Soft-Start Current                                   | V <sub>SS</sub> = 3 V                                                                  | I <sub>SS</sub>              | 12       | 15       | 18        | μΑ             |

| Soft-Start to CS Divider                             | NCP12700CDNR2G<br>Other parts                                                          | K <sub>SS</sub>              |          | 12<br>6  |           |                |

| Soft-Start Discharge Resistance                      |                                                                                        | R <sub>SS(DIS)</sub>         |          |          | 100       | Ω              |

| OSCILLATOR                                           |                                                                                        | •                            |          |          |           |                |

| Oscillator Frequency 1                               |                                                                                        | F <sub>OSC1</sub>            | 185      | 200      | 215       | kHz            |

| Oscillator Frequency 2                               | R <sub>T</sub> = 100 kΩ                                                                | F <sub>OSC2</sub>            | 95       | 100      | 105       | kHz            |

| Oscillator Frequency 3                               | $R_T = 20 \text{ k}\Omega$                                                             | F <sub>OSC3</sub>            | 450      | 500      | 550       | kHz            |

| Oscillator Frequency 4                               | R <sub>T</sub> = 9.09 kΩ                                                               | F <sub>OSC4</sub>            |          | 1000     |           | kHz            |

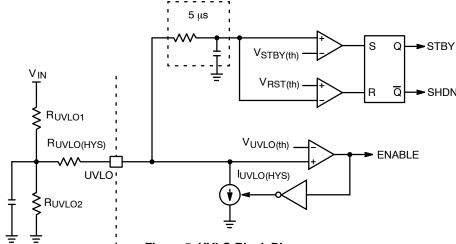

| UNDER-VOLTAGE LOCKOUT (UVLO)                         |                                                                                        | <u> </u>                     |          |          |           |                |

| Standby Threshold                                    | V <sub>UVLO</sub> increasing                                                           | V <sub>STBY(th)</sub>        | 0.35     | 0.5      | 0.65      | V              |

| Reset Threshold                                      | V <sub>UVLO</sub> decreasing                                                           | V <sub>RST(th)</sub>         | 0.3      | 0.45     | 0.6       | V              |

| Standby Hysteresis                                   | V <sub>UVLO</sub> decreasing                                                           | V <sub>STBY(HYS)</sub>       |          | 50       |           | mV             |

| Standby Detection RC Filter                          |                                                                                        | t <sub>STBY(DLY)</sub>       |          | 5        |           | μs             |

| UVLO Threshold                                       | V <sub>UVLO</sub> increasing                                                           | V <sub>UVLO(th)</sub>        | 765      | 800      | 830       | mV             |

| UVLO Threshold Hysteresis                            | V <sub>UVLO</sub> decreasing                                                           | V <sub>UVLO(HYS)</sub>       |          | 15       |           | mV             |

| UVLO Hysteresis Current                              |                                                                                        | I <sub>UVLO(HYS)</sub>       | 4.5      | 5        | 5.5       | μΑ             |

| UVLO Detection Delay Filter                          | V <sub>UVLO</sub> = V <sub>UVLO(th)</sub> – 20 mV                                      | t <sub>UVLO(DLY)</sub>       | 0.5      |          | 1         | μs             |

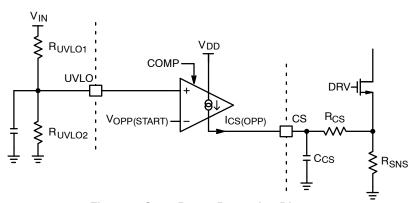

| OVER-POWER PROTECTION (OPP)                          | ,                                                                                      |                              |          |          |           |                |

| UVLO Voltage Above Which OPP Applied                 |                                                                                        | V <sub>OPP(START)</sub>      |          | 1        |           | ٧              |

| OPP Gain                                             |                                                                                        | Gm <sub>(OPP)</sub>          | 135      | 150      | 165       | μ <b>A</b> / V |

| Maximum Current (Operating Point)                    | V <sub>UVLO</sub> = 2.33 V                                                             | I <sub>CS(OPP1)</sub>        | 180      | 200      | 220       | μΑ             |

| Maximum Current                                      | V <sub>UVLO</sub> = 4 V                                                                | I <sub>CS</sub><br>(OPP_MAX) |          | 200      |           | μΑ             |

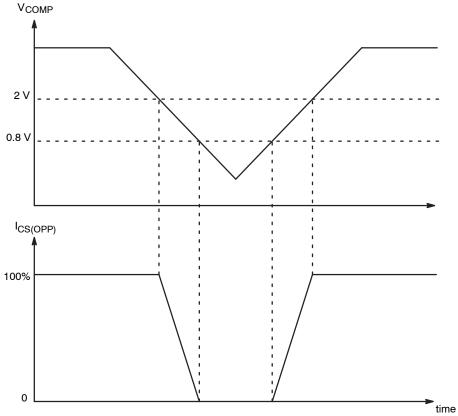

| COMP Threshold Voltage Above<br>Which OPP is Applied |                                                                                        | V <sub>OPP(0%)</sub>         |          | 0.8      |           | V              |

| COMP Threshold Voltage For 100%<br>OPP               |                                                                                        | V <sub>OPP(100%)</sub>       |          | 2        |           | V              |

| GATE DRIVE                                           |                                                                                        |                              |          |          |           |                |

| DRV Rise Time                                        | V <sub>DRV</sub> = 1.2 V to 10.8 V                                                     | t <sub>DRV(rise)</sub>       | 6        | 10       | 15        | ns             |

| DRV Fall Time                                        | V <sub>DRV</sub> = 10.8 V to 1.2 V                                                     | t <sub>DRV(fall)</sub>       | 2.5      | 4        | 10        | ns             |

| DRV Source Current                                   | V <sub>DRV</sub> = 6 V                                                                 | I <sub>DRV(SRC)</sub>        |          | 1.0      |           | Α              |

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ (V_{IN} = 12 \ \text{V}, \ V_{CC} = 12 \ \text{V}, \ V_{COMP} = \text{Open}, \ V_{FLT} = \text{Open}, \ C_{DRV} = 1 \ \text{nF}, \ R_T = 49.9 \text{k}, \ V_{CS} = 0 \ \text{V}, \ V_{SS} = \text{Open}, \ V_{UVLO} = 1.2, \ \text{for typical values} \ T_J = 25^{\circ}\text{C}, \ \text{for min/max values}, \ T_J \ \text{is} - \textbf{40}^{\circ}\text{C} \ \text{to} \ \textbf{125}^{\circ}\text{C}, \ \text{unless otherwise noted})$

| Characteristics              | Test Condition                                                          | Symbol                  | Min   | Тур  | Max   | Unit |

|------------------------------|-------------------------------------------------------------------------|-------------------------|-------|------|-------|------|

| GATE DRIVE                   |                                                                         |                         |       |      |       |      |

| DRV Sink Current             | V <sub>DRV</sub> = 6 V                                                  | I <sub>DRV(SNK)</sub>   |       | 2.8  |       | Α    |

| DRV Clamp Voltage            | V <sub>CC</sub> = 20 V, R <sub>DRV</sub> = 10 kΩ                        | V <sub>DRV(clamp)</sub> | 10    | 12   | 14    | V    |

| Minimum DRV Voltage          | $V_{CC} = V_{CC(OFF)} + 100 \text{ mV},$ $R_{DRV} = 10 \text{ k}\Omega$ | V <sub>DRV(MIN)</sub>   | 6     |      |       | V    |

| FAULT PROTECTION             |                                                                         |                         |       |      |       |      |

| Fault Source Current         |                                                                         | I <sub>FLT</sub>        | 80    | 85   | 90    | μА   |

| OTP Fault Threshold          |                                                                         | V <sub>FLT(OTP)</sub>   | 0.47  | 0.5  | 0.53  | V    |

| OTP Detection Filter Delay   |                                                                         | t <sub>OTP(DLY)</sub>   | 10    | 20   | 30    | μs   |

| OTP Fault Recovery Threshold |                                                                         | V <sub>FLT(REC)</sub>   | 0.846 | 0.9  | 0.954 | V    |

| OVP Fault Threshold          |                                                                         | V <sub>FLT(OVP)</sub>   | 2.8   | 3    | 3.2   | V    |

| OVP Detection Filter Delay   |                                                                         | t <sub>OVP(DLY)</sub>   | 3     | 5    | 7     | μs   |

| Fault Clamp Voltage          | V <sub>FLT</sub> = Open                                                 | V <sub>FLT(CLAMP)</sub> | 1.13  | 1.35 | 1.57  | V    |

| Fault Clamp Resistance       |                                                                         | R <sub>FLT(CLAMP)</sub> |       | 1.6  |       | kΩ   |

| Auto-recovery Timer          |                                                                         | t <sub>AR</sub>         | 0.8   | 1    | 1.2   | s    |

| THERMAL SHUTDOWN             | <u> </u>                                                                |                         |       |      | -     |      |

| Thermal Shutdown             |                                                                         | T <sub>SHDN</sub>       | 150   | 165  | 180   | °C   |

| Thermal Shutdown Hysteresis  |                                                                         | T <sub>SHDN(hys)</sub>  |       | 25   |       | °C   |

#### **Application Information**

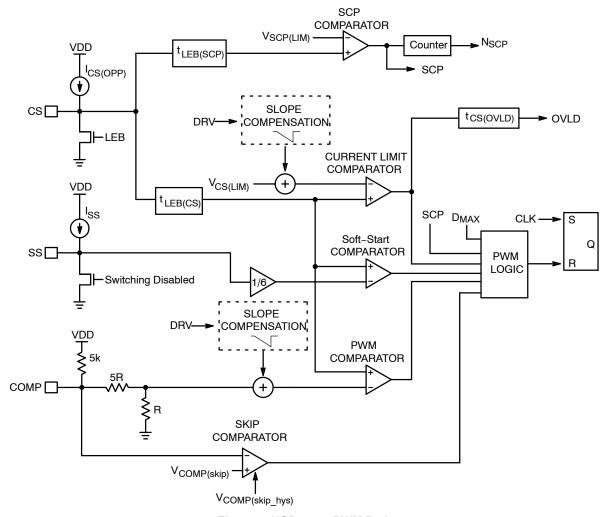

The NCP12700 is a fixed frequency, peak current mode, PWM controller containing all of the features necessary for implementing single-ended power converter topologies. The device features an ultra-wide range, high voltage startup regulator capable of regulating V<sub>CC</sub> across an input voltage range of 9 - 120 V (xDNR2G) or 9 - 200 V (xMTTXG). The controller is designed for high speed operation including a programmable oscillator capable of operating from 100 kHz to 1 MHz and total propagation delays less than 75 ns in the PWM path. The NCP12700 integrates slope compensation to prevent subharmonic oscillations and an Input Voltage Compensation / Over-Power Protection (OPP) feature that limits the converter power delivery capability across input voltage, easing system thermal design. The controller offers an adjustable soft-start, input voltage UVLO protection, and a suite of protection features including cycle-by-cycle current limit and a FLT pin with a NTC interface for system thermal protection. The UVLO pin also features a shutdown comparator which allows for an externally applied pull-down signal to disable switching and bring the controller into a low quiescent state.

### **Ultra-Wide Range HV Startup Regulator**

The NCP12700 features a high voltage startup regulator capable of operating across input voltage ranges of 9–120 V (xDNR2G) or 9–200 V (xMTTXG). The ultra-wide range capability of the regulator allows for direct connection of VIN to the converter input voltage without requiring external components. The regulator's input voltage capabilities support a wide range of industrial, medical, telecom, and transportation applications.

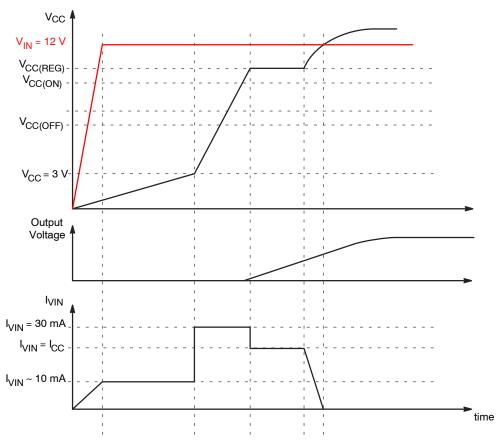

Figure 4 details the operation of the startup regulator. When VIN is applied, the regulator will immediately begin sourcing current to charge  $V_{CC}$ . Initially the startup will supply approximately 10 mA. Once  $V_{CC}$  builds up to  $\sim 3$  V, the control loop for the HV regulator will activate and the source current will be regulated to 30 mA until  $V_{CC}$  reaches the  $V_{CC(REG)}$  level of 8 V. The HV startup is a linear regulator which can continue to supply and regulate  $V_{CC}$  at 8 V. The recommended  $V_{CC}$  capacitance to ensure stability of the regulator is  $1-10~\mu F$ .

While the  $V_{CC}$  voltage is below the  $V_{CC(ON)}$  threshold the controller will remain in a low quiescent state to allow for rapid charging of  $V_{CC}$  and fast startup of the application. Once the  $V_{CC}$  voltage reaches the  $V_{CC(ON)}$  threshold, approximately 200 mV below the  $V_{CC(REG)}$  level, the controller will exit the low quiescent state and begin delivering drive pulses. While the output voltage is building up, the startup regulator will continue to supply the current necessary to maintain  $V_{CC}$  at the  $V_{CC(REG)}$  level. For low input voltage applications, the startup regulator has been designed to guarantee a minimum of 15 mA source capability with 2 V of headroom.

In typical applications an auxiliary winding will be used to provide bias to  $V_{CC}$  once the converter is switching. This allows for the most efficient operation of the system. Once the auxiliary winding pulls the  $V_{CC}$  voltage above  $V_{CC(REG)}$ , the HV regulator will shut off. In normal operation the  $V_{CC}$  voltage can be biased above the voltage at VIN and can support voltages up to 28 V. A  $V_{CC}$  OVP protection feature will trigger at 28 V, disabling switching of the converter to prevent the auxiliary winding voltage from damaging the controller.

Figure 4. Startup Timing Diagram