Keywords: power regulator, regulator control schemes, voltage mode (VM) and current mode (CM) control

## **APPLICATION NOTE 5998**

# CHOOSE THE RIGHT REGULATOR FOR THE JOB: PART 1, REGULATOR CONTROL SCHEMES

By: Don Corey, Principal Member of Technical Staff, Maxim Integrated

Abstract: This application note is Part 1 of a 3-part series on power regulators. It focuses in regulator control schemes, especially voltage mode (VM) and current mode (CM) control. It reviews the duty cycle and load usage for these modes and suggests applications for each mode.

#### Overview

Part 1:Brief review of the importance of duty cycle and load usage. The main focus is regulator control schemes, their types, critical parameters, and compensation schemes. We will finish with a short description of internal versus external FET's.

Part 2: Other topologies besides voltage mode (VM) and current mode (CM) control that incorporate constant on-time, hysteretic, and pulse-frequency modulation (PFM) topologies. Also explains how to select these regulator types for an application.

Part 3: closes with how to select and simulate the optimal regulator for an application.

#### Introduction

It can be a daunting task for an engineer responsible for all aspects of a complex board to choose the optimum regulator for a particular point of load. Several suppliers offer very good solutions, but that does not assure the right regulator for a particular application. For example, a power IC designed for an automotive application may not be a good choice for a consumer product. Portable power applications present a unique set of challenges as the processing power increases while the battery runtime decreases. Equipment with sensitive RF circuitry and low-noise analog front-ends (AFEs) provide an even greater challenge when using switching regulators. In ultrasound equipment where low-level reflected signals from the body are processed, a frequency sync input may be a hard and fast requirement to control the power-supply switching harmonics. In higher current applications efficiency is often the most important requirement. Ultimately, an engineer must decide what power features are critical to the application and then select a regulator designed for those requirements.

## The Devil Is in the Details

When choosing regulators for portable applications, the duty cycle and load usage are important details. Load usage refers to how the loads behave. Under normal operation, are the loads constant? Do they vary frequently between minimum to maximum full-scale currents? The duty-cycle operation is the ratio of how long the equipment is active to the time that it spends in an idle or low-current state.

Why is all this important? Let's look at some details. Load usage is important as it helps determine the required quiescent current  $(I_Q)$ . For example, does the regulator spend most of its time fully loaded? Then choosing a regulator with ultra-low  $I_Q$  may not be the most important specification, especially if the average load current is substantially higher than the regulator's rated  $I_Q$ . If this is the case and the operation duty cycle is low, and if the regulator's output is not a keep-alive voltage and can be shutdown during idle and sleep modes, then choosing a regulator with low shutdown current may be more important. If, moreover, the duty cycle is low and the regulator must be kept on, then selecting a regulator with low  $I_Q$  in a battery-operated product is important. Additionally, if the regulator during normal operation spends as much time servicing light loads as it does servicing full loads, then ultra-low operating current is very important for optimizing its efficiency and battery runtime.

### Choosing the Control Scheme

Regulator control schemes have a very important role in your decision. To complicate matters, there are several types of regulator topologies. Hysteretic or PFM schemes are typically used where efficiency needs to be optimized at light loads. Pulse-width modulation (PWM) topologies are needed when lower output noise is required because these converters operate at fixed frequencies and are, therefore, easier to filter. PWM contrasts with PFM topologies in which the switching frequencies decrease when lightly loaded, while the switching frequency increases when load current increases.

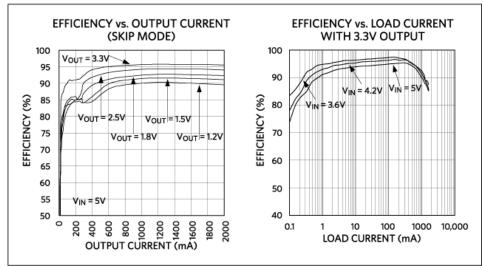

Some regulators offer dual-mode operation, thus switching between PWM and skip operation modes. In skip mode overall power efficiency improves at light loads versus using PWM mode. **Figure 1** is a typical efficiency plot for a switching regulator, here the MAX15053, operating in skip mode. Note that the typical operating current is 1.53mA. Therefore, if the application's operation duty cycle is low and the load currents are close to their maximum, this switching regulator is a good choice for a portable application. There is a caveat-this is all accurate as long as the regulator can be placed in shutdown during idle states. However, whenever the operation duty cycle is low and the regulator is always on during idle and sleep states, then a step-down regulator with low operating current is more appropriate. Figure 1 also shows that the operation current for the MAX1556 step-down regulator in skip mode is typically 16µA. A side-by-side efficiency comparison between these two parts reveals that the MAX1556 would be a better choice to extend battery runtime if the regulator must be active 100% of the time while the system is powered on.

Figure 1. Efficiency for the MAX15053 switching regulator (left) versus the MAX1556 step-down regulator (right). Data shows that the MAX1556 would be a better choice for always-on power in standby mode.

Standby current is important for portable applications, and the regulator search can be simplified by using the suppliers' website parametric search tool (**Figure 2**). By selecting a few key parameters, such as internal switch, minimum voltage input, maximum voltage input, and  $I_{CC}$  (mA), it is relatively easy to sort through many part options and quickly select the right regulator for the application. In the example below the minimum and maximum input voltage were set and the internal switch box checked. The design engineer can set the  $I_{CC}$  (mA) slider to the lowest setting offered. Now the designer sees the two best matches from the total parts.

Figure 2. Parametric search tool used to narrow the down the choices.

## Current-Mode versus Voltage-Mode Control

Let's now spend some time examining the different control topologies.

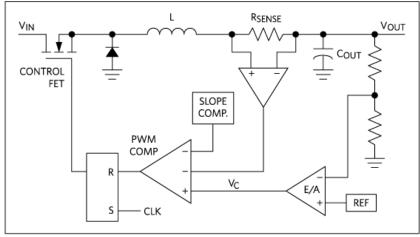

There are two control topologies available for PWM switching regulators: voltage mode (VM)  $^{2,4}$  and current mode (CM).  $^{1,2,3}$  The CM regulator uses the inductor current as part of the feedback loop and the voltage feedback loop. The inductor current and the output-voltage-error signal are input signals to the PWM modulator. **Figure 3** shows a simplified schematic of peak CM control, where the peak inductor current is controlled along with the output voltage. The inductor current is sensed by some means and compared to a control voltage, V<sub>C</sub>, which is derived from the output voltage error. Slope compensation is needed for CM control to prevent subharmonic oscillations for duty cycles greater than 50%.

Figure 3. Current mode (CM) control.

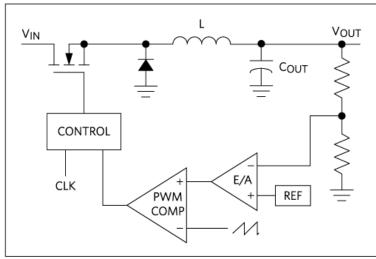

Voltage-mode control has been used for a long time since the first switching regulator designs became available. Voltage mode has a single voltage feedback path; PWM is performed by comparing the voltage error signal with a constant ramp waveform. **Figure 4** shows this basic configuration.

Figure 4. Voltage-mode (VM) control.

## Advantages of CM Control

So let's briefly dig into the advantages and disadvantages of both topologies, starting with the CM topology.

Why current mode? In taking a closer look at the current control-loop response we find that when the control FET is on, the current through R<sub>SENCE</sub> provides a voltage ramp from the output of the current-sense amp. The voltage ramp is proportional to the ramp current in the inductor. This slope-compensated voltage ramp is then compared to the output of the error amp. The control FET will be on until the voltage sensed

from the inductor current equals the control voltage,  $V_C$ . When these two voltages are equal, the control FET is turned off. The next switching cycle is started by setting the RS flip-flop from a fixed-frequency clock signal shown in Figure 3. So, basically the voltage control loop determines the level at which the current loop regulates the peak current through the control FET switch and inductor. Without drilling down into the math, CM control eliminates the inductor pole and second-order characteristic found in VM control because the inner-current control loop includes the output filter inductor. The outer voltage control loop, therefore, only has the single pole of the output filter and load resistance. You can think of a CM converter as a current source, supplying and regulating current to a single pole formed by the output capacitor in parallel with the load impedance at frequencies below the current-loop bandwidth. What does all this mean? Basically, it means that compensating a CM controller for stability is a lot easier than doing it with a VM controller.

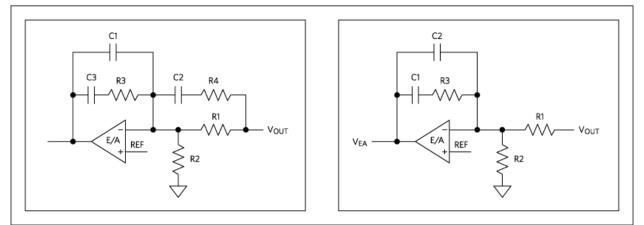

Now let's talk about compensation schemes. **Figure 5** illustrates the difference between the two typical compensation networks used in these two control topologies. Voltage-mode compensation<sup>4</sup> (Type III) on the left requires a more complex compensation network than the current-mode compensation (Type II)<sup>5</sup> on the right where C2 may not even be needed.

Figure 5. Schematics showing VM compensation (left) versus CM compensation (right). With CM compensation, C2 may not be needed.

One of the disadvantages early on of the CM control scheme was that it required accurate current sensing<sup>2</sup> which, in turn, caused a slight power loss in the sensing element. Today's integrated power solutions eliminate the need for external current-sense resistors; the current sensing is performed internally by using the  $R_{DS(ON)}$  of the high-side FET. In addition to a simple compensation<sup>2</sup> network, the CM converter offers superb line regulation, very good transient response to large load changes, and cycle-to-cycle current limiting because the current is sensed each timing cycle.

Line regulation is defined as the amount that the output voltage changes with a change in input voltage. It is related to the gain of the controlto-output transfer function. Since the gain of the control-to-output transfer function for the CM topology is independent of the input voltage, the line regulation is very good. Also for this topology a single pole operates with less phase/time lag, so a converter with peak CM control will have better transient response than a converter with VM PWM control. When examining the control-to-output transfer function of the VM topology, the input voltage has a direct impact on the gain and the line regulation will be degraded. Today's VM converters overcome this by employing voltage feed-forward techniques that change the slope of the PWM ramp based on the input voltage. **Table 1** outlines the advantages/disadvantages<sup>2</sup> of both topologies.

So why choose VM versus CM? Since the CM design requires two control loops and greater circuit complexity versus that of VM, it may be more cost effective to choose a regulator with VM control. Historically, with a wide input-voltage operating range especially under low-line/lightload conditions, the current ramp slope may be too shallow for stable CM PWM operation. This limitation has been greatly improved by new devices like the MAX17500/MAX17501/MAX17502/MAX17503 and MAX17504 family of high-voltage CM converters.

| <b>Table Summary</b> | of | VM | Control | versus | СМ | Control |

|----------------------|----|----|---------|--------|----|---------|

|----------------------|----|----|---------|--------|----|---------|

|                             | Current Mode                                                                                              | Voltage Mode                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Compensation                | Simple compensation network                                                                               | Complex compensation network                                                            |

| DCM and<br>CCM<br>operation | Transitions from critical conduction mode (CCM) to discontinuous conduction mode (DCM) are not a problem. | Harder to design a compensator that provides good performance in both conduction modes. |

| Line rejection              | Very good line regulation                                                                                 | Need voltage feed forward                                                               |

| Current sensing             | Needed                                                                                                    | Not needed                                                                              |

| Subharmonic oscillations | Current-mode control can be unstable when the converter's duty cycle approaches 50%. Modern converters employ internal slope compensation that eliminates both these effects and the need for power-supply design expertise to account for these effects. | Not applicable                                                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transient response       | Since CM control senses a change in load cycle; the error<br>amplifier does not need to react quickly so the loop can make a<br>correction.                                                                                                               | In VM control a load current change must change the<br>output voltage before the error amplifier can react and<br>make a correction. VM control is slower to respond to<br>very high-speed load transients than is CM control. |

## What Is Slope Compensation?

Although most modern integrated converters include built-in slope compensation, it is important to understand why slope compensation is needed.

Assume that a step-down converter is operating in continuous conduction mode (CCM). This means that the current in the inductor never falls to zero, and the duty cycle is about 75% at heavy load with only the output current as the ramp signal to the comparator (i.e., no slope compensation). A load transient to light load will then cause the current control loop to turn off the control FET switch early. Since the duty cycle is at 75%, there is little time for the inductor current to decay and the flux in the inductor core to reset itself. Meanwhile, the load voltage determines the inductor's falling slope. As long as the load is not shorted, the current in the output inductor will take time to ramp down to the lower threshold value at the PWM comparator. When the clock initiates the next cycle, the switch never turns on because the current is still too high. (Alternatively, it turns on very briefly at the minimum duty cycle of the controller.) If the current is really high, the next cycle may see the same conditions and remain effectively off.

This condition will make the converter oscillate at some subharmonic of the PWM switching frequency. Slope compensation provides a means to bring the ramp down to zero during the short dead time. The ramp of the internal clock signal is summed with the sensed current waveform. There will still be very short pulses for overcurrent conditions, but by summing the clock signal with the current signal, this subharmonic oscillation has been resolved.

## Synchronous versus Asynchronous Rectification

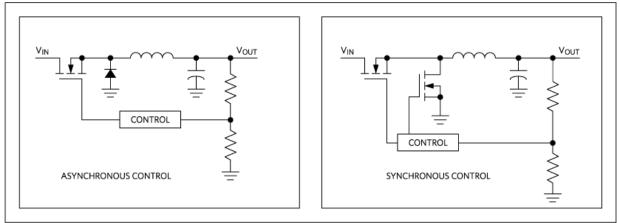

Taking a closer look at the power stage of a typical DC/DC converter, we see that there are two types of output stages (**Figure 6**). A converter with both high-side and low-side FETs is commonly referred to as having synchronous rectification; the control block of the DC/DC converter will synchronize the turn on/off times of both FETs. This action optimizes and prevents overlapping of these FETs so that neither FET is conducting at the same time. The high-side FET conducts at  $V_{OUT}/V_{IN} \times 1/f_{sw}$ ; the low-side FET conducts at 1 -  $V_{OUT}/V_{IN} \times 1/f_{sw}$ , where fsw is the switching frequency of the converter. In general for low-duty-cycle applications asynchronous converters may not meet board power-efficiency goals, as the conduction power loss can be dominated by the I  $\times V_{DIODE}$  power loss versus the low-side R<sub>DS(ON)</sub>  $\times$  I power loss of a synchronous converter.

When choosing a part with synchronous rectification, look closely at the application. For example, if the application is to convert 5V to 2.5V, then a regulator with a rating of 14V may not be optimal as it could be designed for a distributed 12V power bus commonly found in telecom and server applications. As such, the internal high-side FET may have a higher  $R_{DS(ON)}$ , optimized for typical duty cycles that are less than 10% for 1V and lower core voltages.

For this example, the 12V regulator's FETs can be optimized for a much lower duty cycle in which the  $R_{DS(ON)}$  is optimized for the low-side FET where conduction power losses dominate; the high-side FET has higher  $R_{DS(ON)}$  but much lower gate charge where the switching power losses tend to dominate. Thus, to convert 5V to 2.5V, the duty cycle is 50%. Choosing a part with a maximum rating of 6V may be the better choice. Typically, the majority of step-down converters designed for 5V and 12V systems will employ a synchronous-rectifier output stage. Asynchronous rectification stages that use Schottky diodes in place of the low-side FET seem to be more common in industrial applications when voltage levels are at least 24V and higher.

Figure 6. Asynchronous versus synchronous control.

Newer parts like the MAX17501–MAX17504 mentioned above integrate both high-side and low-side FETs. They have a maximum voltage input rating of 60V that allows for increased efficiency in industrial applications where the DC voltage bus is 24V or higher.

## Internal versus External FETs

There is no one-size-fits-all regulator optimized for all possible power rails. Consequently, sometimes a designer who wishes to optimize efficiency for a given application will choose a DC/DC controller that requires external FETs. At higher power levels when creating sub-1V power rails from a 12V, FET selection is critical. Thus, choosing a high-side FET with higher R<sub>DS(ON)</sub> and low gate charge can optimize overall efficiency when duty cycles are low. Further, it may be necessary to use two or more FETs in parallel to decrease the conduction loses, while keeping the switching losses at a minimum for the low-side FET.

The References at the end provide a good starting point for the selection criteria of external FETs for DC/DC controllers.

### Conclusion

Part 1 provides a better understanding of the design trade-offs when selecting the right regulator. Understanding the application is critical for choosing the optimal regulation solution. By explaining the differences between voltage mode (VM) and current mode (CM) control we help the reader choose the best topology for the application. The reader will also benefit from a description of the performance-versus-cost trade–offs between synchronous versus asynchronous rectification. Finally, we outlined why it may be advantageous to choose a controller that uses external FETs. This application note targets the board designer who may not have the luxury of utilizing in-house power supply engineers.

The second application note in this series, Choose the Right Regulator for the Job: Part 2, discusses and contrasts several control topologies: PFM, hysteretic, COT, and skip mode.

In Part 3, we will provide the basic equations to help a designer choose the best regulator and optimize the surrounding components for the total regulator solution, and provide a part selection and simulation example that illustrates the topics discussed in both prior application notes.

#### References

- 1. Harman, Mark, "Inside Current Mode Control," POWER/designer, No. 106, href="http://application-notes.digchip.com/006/6-8586.pdf .

- Ridley, Dr. Ray, "Current Mode or Voltage Mode?" Switching Power Magazine, Oct 2000, http://encon.fke.utm.my/nikd/latest/OctCurrentMode.pdf.

- 3. Schimel, Paul, "Peak Current Mode Control Will Never Die!??" Electronic Design, Apr 7 2011, http://electronicdesign.com/power/peakcurrent-mode-control-will-never-die.

- 4. Timothy Hegarty, "Voltage-mode control and compensation: Intricacies for buck regulators," EDN, June 30 2008, http://www.edn.com/design/analog/4326882/Voltage-mode-control-and-compensation-Intricacies-for-buck-regulators.

- 5. Zimnik, Marcus, Comparison of PWM Voltage and Current Mode Control Schemes vs. Improved Hysteretic Mode Control in Switch Mode Power Supplies (SMPS) http://u.dianyuan.com/bbs/u/0/1066039498.pdf.

- Elbanhawy, Alan, "A simple guide to selecting power MOSFETS," EDN, November 22, 2001, http://www.edn.com/design/components-and-packaging/4341997/A-simple-guide-to-selecting-power-MOSFETs.

A similar version of this application note appeared February 2015 on HOW2POWER.com.

| Related Parts |                                                                                                   |              |

|---------------|---------------------------------------------------------------------------------------------------|--------------|

| MAX15053      | High-Efficiency, 2A, Current-Mode Synchronous, Step-Down Switching Regulator                      | Free Samples |

| MAX1556       | 16 $\mu$ A I <sub>Q</sub> , 1.2A PWM Step-Down DC-DC Converters                                   | Free Samples |

| MAX17500      | Current-Mode PWM Controllers with Programmable Switching Frequency                                | Free Samples |

| MAX17501      | 60V, 500mA, Ultra-Small, High-Efficiency, Synchronous Step-Down DC-DC Converter                   | Free Samples |

| MAX17502      | 60V, 1A, Ultra-Small, High-Efficiency, Synchronous Step-Down DC-DC Converter                      | Free Samples |

| MAX17503      | 4.5V-60V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation | Free Samples |

| MAX17504      | 4.5V–60V, 3.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation | Free Samples |

## More Information

For Technical Support: https://www.maximintegrated.com/en/support

For Samples: https://www.maximintegrated.com/en/samples Other Questions and Comments: https://www.maximintegrated.com/en/contact

Application Note 5998: https://www.maximintegrated.com/en/an5998 APPLICATION NOTE 5998, AN5998, AN 5998, APP5998, Appnote5998, Appnote 5998

© 2014 Maxim Integrated Products, Inc.

The content on this webpage is protected by copyright laws of the United States and of foreign countries. For requests to copy this content, contact us.

Additional Legal Notices: https://www.maximintegrated.com/en/legal