# Platform Flash XL Configuration and Storage Device

**User Guide**

UG438 (v3.1) January 12, 2021

#### Notice of Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at <a href="https://www.xilinx.com/legal.htm#tos">www.xilinx.com/legal.htm#tos</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at <a href="https://www.xilinx.com/legal.htm#tos">www.xilinx.com/legal.htm#tos</a>.

© Copyright 2008–2021 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

### **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                          |  |  |  |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 03/28/2008 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                           |  |  |  |

| 05/14/2008 | 1.1     | Added Figure 2-1, page 16 and Figure 3-1, page 32 footnotes. Added "Master SelectMAP Configuration Mode" in Chapter 3. Changed Chapter 3 title to "Alternate Configuration Modes." Added updates highlighting recommended configuration mode (Slave SelectMAP).                   |  |  |  |

| 12/10/2008 | 1.2     | Chapter 1: Added cross reference to <i>Virtex-5 FPGA Configuration User Guide</i> . Removed NC and DU signals from Table 1-2. Updated description of I/O power supply to include support of 2.5V.                                                                                 |  |  |  |

|            |         | Chapter 2: Updated chapter title and "Slave SelectMAP Configuration Mode." Updated Figure 2-1, including note 7, and added notes 10 and 11. Added Table 2-1 and Figure 2-2.                                                                                                       |  |  |  |

|            |         | Chapter 3: Updated "Master BPI-Up Configuration Mode." Added notes 9 and 10 to and updated Figure 3-1. Updated table headings and added $\overline{L}$ (latch enable) signal to Table 3-1. Updated "FPGA BPI-Up Configuration from Platform Flash XL." Updated Figure 3-3 title.  |  |  |  |

|            |         | Chapter 5: Deleted note from "Preparing a Programming File." Updated iMPACT software version. Added "Step 3: Select the XCF128X Device."                                                                                                                                          |  |  |  |

|            |         | Chapter 6: Updated Figure 6-1. Updated note in "Minimum Requirements for Indirect In-System Programming." Updated iMPACT software version. Interchanged "Step 7: Select iMPACT Programming Properties" and "Step 6: Invoke the iMPACT Program Operation." Updated "Expectations." |  |  |  |

|            |         | Added Chapter 4, "Calculating Configuration Time" and Chapter 8, "FPGA User Design Recommendations."                                                                                                                                                                              |  |  |  |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/14/2009 | 2.0     | Added support for Virtex-6 FPGAs. Updated iMPACT software version. Updated "Overview." Added Table 1-1, which contains configuration flash information for Virtex-5 and Virtex-6 devices. Updated "Family Description," including Figure 1-1 and Table 1-2. Updated "Slave SelectMAP Configuration Mode" and "Slave SelectMAP Configuration from Platform Flash XL."                                            |

|            |         | Updated Figure 2-1 and its associated notes. Added Figure 2-2 and its associated notes. Updated Table 2-1. Updated Figure 2-3 and its associated notes.                                                                                                                                                                                                                                                         |

|            |         | Updated "Master BPI-Up Configuration Mode," Figure 3-1 and its associated notes, Table 3-1, "FPGA BPI-Up Configuration from Platform Flash XL," Figure 3-2 and its associated notes, "Master SelectMAP Configuration Mode," and notes relating to Figure 3-3.                                                                                                                                                   |

|            |         | Updated Chapter 4, "Calculating Configuration Time."                                                                                                                                                                                                                                                                                                                                                            |

|            |         | Updated "Using the iMPACT Graphical Software."                                                                                                                                                                                                                                                                                                                                                                  |

|            |         | Updated Figure 6-1. Deleted Frequency column from Table 6-1. Updated "Minimum Requirements for Indirect In-System Programming." Updated "Xilinx Cable Connections" and "Effect of Indirect Programming on the Rest of the System." Removed Table 6-2; information is available in <a href="DS593">DS593</a> , Platform Cable USB II Data Sheet Updated steps and GUI screen shots in "iMPACT Programming Flow." |

|            |         | Added Chapter 7, "System Considerations."                                                                                                                                                                                                                                                                                                                                                                       |

|            |         | Added "Re-Using Configuration Pins for Other Purposes."                                                                                                                                                                                                                                                                                                                                                         |

|            |         | Updated "FPGA Designs Not Accessing Platform Flash XL after Configuration" and "FPGA Designs Accessing Platform Flash XL after Configuration."                                                                                                                                                                                                                                                                  |

|            |         | Updated Table 8-2.                                                                                                                                                                                                                                                                                                                                                                                              |

| 08/05/2015 | 3.0     | This product is obsolete/discontinued per XCN15008. Updated Notice of Disclaimer.                                                                                                                                                                                                                                                                                                                               |

| 01/12/2021 | 3.1     | Removed obsolete banner. See product discontinuance retraction in XCN15008 for device availability.                                                                                                                                                                                                                                                                                                             |

| form Flash XL Configurati | on & Storage Device | www.xilinx.com | <br>UG438 (v3.1) Janu | ary 12, 20 |

|---------------------------|---------------------|----------------|-----------------------|------------|

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

|                           |                     |                |                       |            |

# Table of Contents

| Revision History                                         | . 2 |

|----------------------------------------------------------|-----|

| Preface: About This Guide                                |     |

| Summary                                                  | . 7 |

| Guide Contents                                           |     |

| Additional Resources                                     | . 7 |

| General                                                  |     |

| Software                                                 | _   |

| Additional Documentation                                 |     |

| Conventions                                              |     |

| TypographicalOnline Document                             | . 9 |

| Chapter 1: Overview                                      |     |

| Family Description                                       | 12  |

| Chapter 2: High-Speed Configuration                      |     |

| Slave SelectMAP Configuration Mode                       | 15  |

| Slave SelectMAP Configuration from Platform Flash XL     | 27  |

| Chapter 3: Alternate Configuration Modes                 |     |

| Master SelectMAP Configuration Mode                      | 31  |

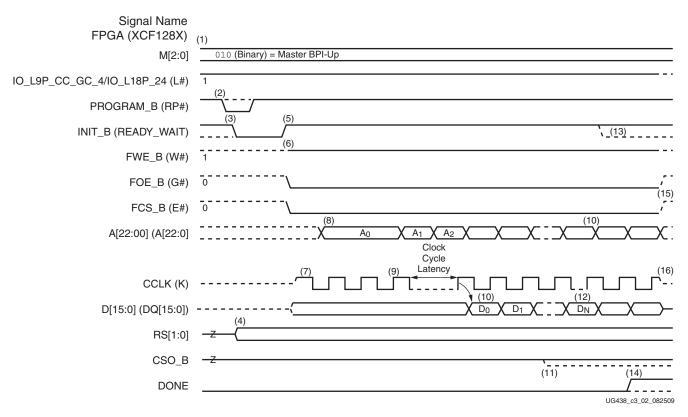

| Master BPI-Up Configuration Mode                         |     |

| FPGA BPI-Up Configuration Signals                        |     |

| FPGA BPI-Up Configuration from Platform Flash XL         |     |

| Waster Wode Considerations                               | 45  |

| Chapter 4: Calculating Configuration Time                |     |

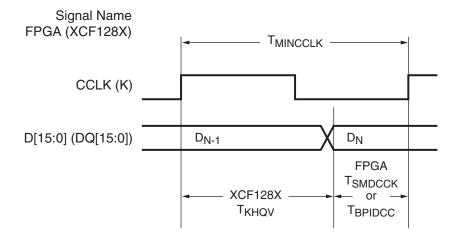

| Determining the Maximum Configuration Clock Frequency    |     |

| Slave SelectMAP Maximum Configuration Clock Frequency    | 46  |

| Master SelectMAP/BPI Maximum Configuration Clock Setting |     |

| Determining Configuration Time.                          | 47  |

| Chapter 5: Platform Flash XL File Generation             |     |

| Preparing a Programming File                             | 49  |

| Using the PROMGen Command-Line Software                  | 49  |

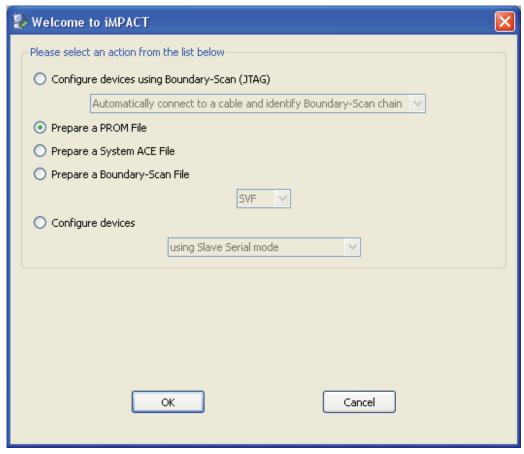

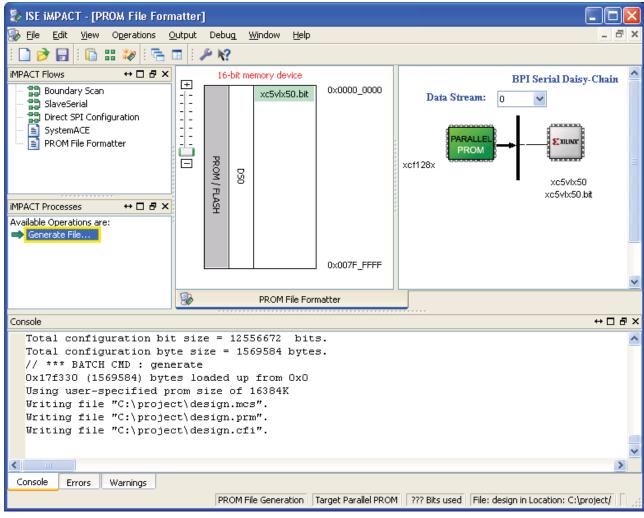

| Using the iMPACT Graphical Software                      |     |

| Step 1: Prepare a PROM File                              |     |

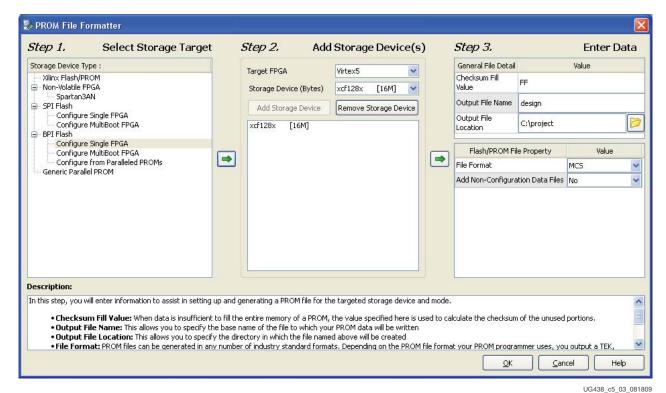

| Step 3: Select the XCF128X Device                                | 52 |

|------------------------------------------------------------------|----|

| Step 4: Specify Output PROM File Name and Location               |    |

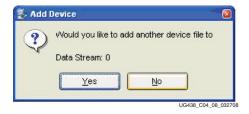

| Step 5: Notification to Add a Device to the PROM File            |    |

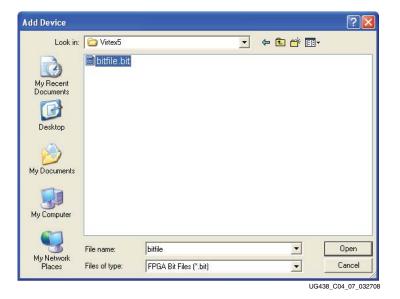

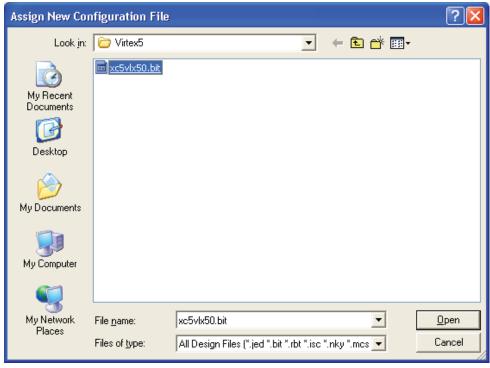

| Step 6: Select the FPGA Bitstream File to Add                    |    |

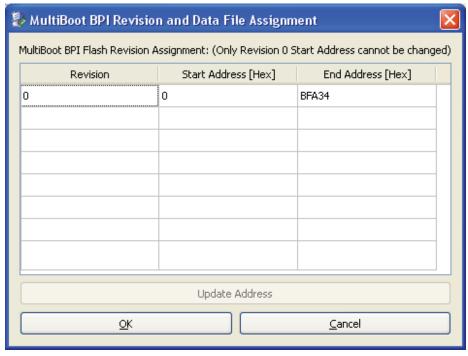

| Step 7: Generate File Operation                                  |    |

|                                                                  |    |

| Chapter 6: Programming Platform Flash XL                         |    |

| Programming Platform Flash XL During Prototyping                 | 57 |

| Minimum Requirements for Indirect In-System Programming          |    |

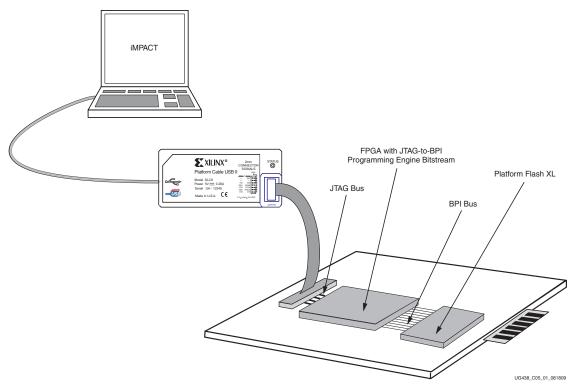

| Xilinx Cable Connections                                         |    |

| iMPACT Programming Flow                                          | 59 |

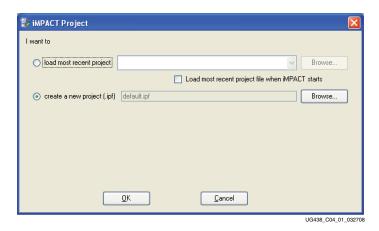

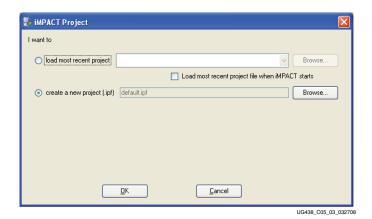

| Step 1: Create a New Project for Indirect In-System Programming  |    |

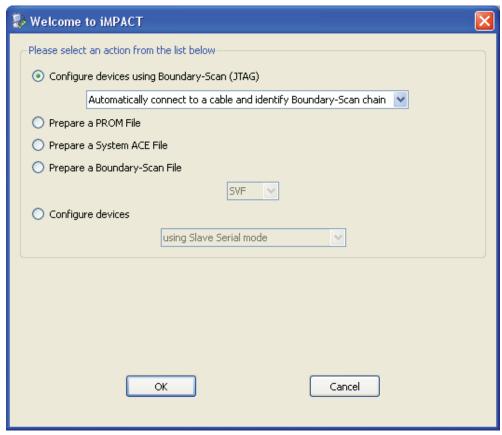

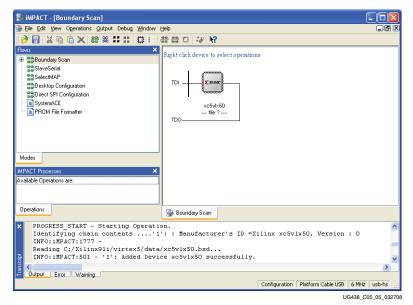

| Step 2: Configure Devices Using the JTAG-to-BPI Method           |    |

| Step 3: Assign the FPGA Configuration File                       |    |

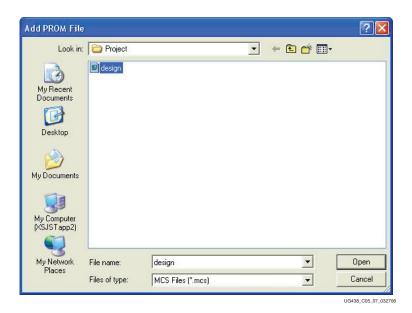

| Step 4: Add a PROM File for Indirect Programming                 |    |

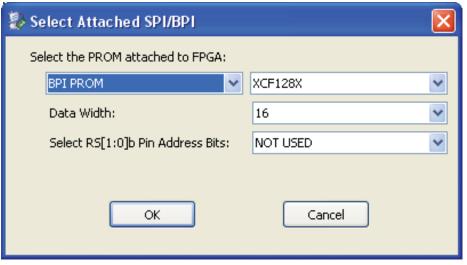

| Step 5: Select Xilinx XCF128X Device Part Number                 |    |

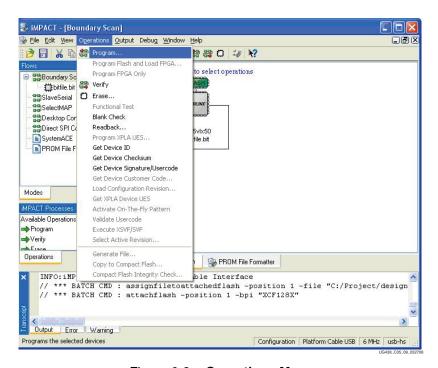

| Step 6: Invoke the iMPACT Program Operation                      | 64 |

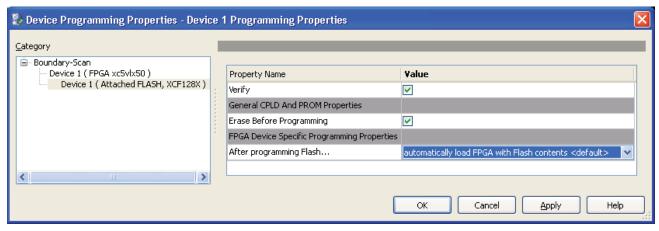

| Step 7: Select iMPACT Programming Properties                     | 65 |

| Expectations                                                     | 65 |

| iMPACT Operations and Programming Times                          |    |

| Effect of Indirect Programming on the Rest of the System         | 66 |

| Pull-Up and Pull-Down Consideration                              |    |

| Production Programming Solutions                                 |    |

| Device Programmers                                               |    |

|                                                                  | -  |

| Chapter 7: System Considerations                                 |    |

| •                                                                |    |

| Platform Flash XL VDDQ Power Budget                              | 69 |

|                                                                  |    |

| Chapter 8: FPGA User Design Recommendations                      |    |

| FPGA Designs Not Accessing Platform Flash XL after Configuration | 71 |

| Re-Using Configuration Pins for Other Purposes                   | 72 |

| FPGA Designs Accessing Platform Flash XL after Configuration     | 72 |

| FPGA Design Preparation for Asynchronous Read Mode Access        |    |

| FPGA Design Preparation for FPGA Reconfiguration                 |    |

# About This Guide

## **Summary**

This guide describes the Platform Flash XL feature set, demonstrates the common configuration mode setups supported, and provides the software flows necessary to generate the programming files and indirectly program the device in-system. More information on Platform Flash XL is available online in <a href="DS617">DS617</a>, Platform Flash XL High-Density Configuration and Storage Device.

### **Guide Contents**

This manual contains the following chapters:

- Chapter 1, "Overview," provides a brief description of key features of Platform Flash XL.

- Chapter 2, "High-Speed Configuration," describes the most popular setup for high-performance applications.

- Chapter 3, "Alternate Configuration Modes," describes the BPI-Up configuration mode setup and the Master SelectMAP configuration mode considerations.

- Chapter 4, "Calculating Configuration Time," describes the considerations and parameters used to determine the minimum configuration time.

- Chapter 5, "Platform Flash XL File Generation," demonstrates the steps required to prepare programming files in popular PROM formats.

- Chapter 6, "Programming Platform Flash XL," describes the flow used to program the device indirectly using iMPACT software.

- Chapter 7, "System Considerations," provides V<sub>DDQ</sub> power budget estimates from a real example test board.

- Chapter 8, "FPGA User Design Recommendations," describes recommendations for FPGA designs that use Platform Flash XL for storage after configuration.

### Additional Resources

#### General

To find additional documentation, see the Xilinx<sup>®</sup> website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

### Software

The Xilinx PROMGen and iMPACT software are available with the main Xilinx ISE<sup>®</sup> Foundation<sup>TM</sup> software or with the downloadable Xilinx ISE WebPACK<sup>TM</sup> software packages.

- ISE Foundation software

http://www.xilinx.com/ise/logic\_design\_prod/foundation.htm

- The Xilinx ISE software manuals are available at: http://www.xilinx.com/support/software\_manuals.htm

### Hardware

Information regarding the Xilinx cables are found on the Xilinx Configuration Solutions website:

http://www.xilinx.com/products/design\_resources/config\_sol/

See the ISE iMPACT software manuals for supported Xilinx cables.

### **Additional Documentation**

- <u>DS152</u>, Virtex-6 FPGA Data Sheet: DC and Switching Characteristics

This data sheet contains the DC and switching characteristic specifications for the Virtex-6 family.

- UG360, Virtex-6 FPGA Configuration User Guide

This all-encompassing configuration guide includes chapters on configuration interfaces (serial and SelectMAP), bitstream encryption, Boundary-Scan and JTAG configuration, reconfiguration techniques, and readback through the SelectMAP and JTAG interfaces.

- UG191, Virtex-5 FPGA Configuration User Guide

- This all-encompassing configuration guide includes chapters on configuration interfaces (serial and SelectMAP), bitstream encryption, Boundary-Scan and JTAG configuration, reconfiguration techniques, and readback through the SelectMAP and JTAG interfaces.

- <u>DS202</u>, Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

This data sheet contains the DC and switching characteristic specifications for the Virtex-5 family.

- DS617, Platform Flash XL High-Density Configuration and Storage Device

This data sheet describes the Platform Flash XL configuration and storage device optimized for the Virtex-5 FPGA.

### **Conventions**

This document uses the following conventions. An example illustrates each convention.

# **Typographical**

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                               | Example                                                                                            |  |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Courier font        | Messages, prompts, and program files that the system displays                                                | speed grade: - 100                                                                                 |  |

| Courier bold        | Literal commands that you enter in a syntactical statement                                                   | ngdbuild design_name                                                                               |  |

| Helvetica bold      | Commands that you select from a menu                                                                         | File → Open                                                                                        |  |

|                     | Keyboard shortcuts                                                                                           | Ctrl+C                                                                                             |  |

|                     | Variables in a syntax statement for which you must supply values                                             | ngdbuild design_name                                                                               |  |

| Italic font         | References to other manuals                                                                                  | See the <i>Development System Reference Guide</i> for more information.                            |  |

|                     | Emphasis in text                                                                                             | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |  |

| Square brackets []  | An optional entry or parameter. However, in bus specifications, such as <b>bus</b> [7:0], they are required. | ngdbuild [option_name] design_name                                                                 |  |

| Braces { }          | A list of items from which you must choose one or more                                                       | lowpwr ={on off}                                                                                   |  |

| Vertical bar        | Separates items in a list of choices                                                                         | lowpwr ={on off}                                                                                   |  |

| Vertical ellipsis   | Repetitive material that has been omitted                                                                    | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |  |

| Horizontal ellipsis | Repetitive material that has been omitted                                                                    | allow block block_name loc1 loc2 locn;                                                             |  |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                         | Example                                                                                              |  |

|-----------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| Plan (and             | Cross-reference link to a location                     | See the section "Additional Resources" for details.                                                  |  |

| Blue text             | in the current document                                | Refer to "Title Formats" in Chapter 1 for details.                                                   |  |

| Red text              | Cross-reference link to a location in another document | See Figure 2-5 in the <i>Virtex-5 FPGA User Guide</i> .                                              |  |

| Blue, underlined text | Hyperlink to a website (URL)                           | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed specifications. |  |

# Overview

This guide supplements <u>DS617</u>, *Platform Flash XL High-Density Storage and Configuration Device*, giving specific user information on device features and usage modes.

The Platform Flash XL (XCF128X) configuration and storage device is optimized for use with Virtex®-5 and Virtex-6 FPGAs (see Table 1-1). The Platform Flash XL does not support older Virtex families, Spartan® families, or AES encrypted bitstreams. See <u>UG161</u>, *Platform Flash PROM User Guide*, for alternative Platform Flash PROMs.

For bitstream length (bits), see <u>UG360</u>, *Virtex-6 FPGA Configuration User Guide* or <u>UG191</u>, *Virtex-5 FPGA Configuration User Guide*.

Single-chip Platform Flash XL provides a high-density non-volatile storage with the industry's highest performing configuration, ease-of-use and flexibility within a small footprint package.

With in-system configuration speeds up to 800 Mb/s, Platform Flash XL is ideally suited for high-performance PCI Express<sup>®</sup> technology applications used in optical and enterprise networking, WiMAX digital front-end and baseband processing, video broadcast equipment, and medical ultrasound and scanners.

Table 1-1: Configuration Flash for Virtex-5 and Virtex-6 FPGAs

| FPGA           | Configuration Flash                                                     |  |  |  |  |

|----------------|-------------------------------------------------------------------------|--|--|--|--|

| Virtex-6 FPGAs | Virtex-6 FPGAs                                                          |  |  |  |  |

| XC6VLX75T      | XCF128X                                                                 |  |  |  |  |

| XC6VLX130T     | XCF128X                                                                 |  |  |  |  |

| XC6VLX195T     | XCF128X                                                                 |  |  |  |  |

| XC6VLX240T     | XCF128X                                                                 |  |  |  |  |

| XC6VHX250T     | XCF128X                                                                 |  |  |  |  |

| XC6VHX255T     | XCF128X                                                                 |  |  |  |  |

| XC6VHX380T     | XCF128X                                                                 |  |  |  |  |

| XC6VHX565T     | See <u>UG360</u> , Virtex-6 FPGA Configuration User Guide for BPI flash |  |  |  |  |

| XC6VSX315T     | XCF128X                                                                 |  |  |  |  |

| XC6VLX365T     | XCF128X                                                                 |  |  |  |  |

| XC6VSX475T     | See <u>UG360</u> , Virtex-6 FPGA Configuration User Guide for BPI flash |  |  |  |  |

| XC6VLX550T     |                                                                         |  |  |  |  |

| XC6VLX760      |                                                                         |  |  |  |  |

Table 1-1: Configuration Flash for Virtex-5 and Virtex-6 FPGAs (Cont'd)

| Virtex-5 FPGAs           XC5VLX30         XCF128X           XC5VLX50         XCF128X           XC5VLX85         XCF128X           XC5VLX110         XCF128X           XC5VLX155         XCF128X           XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX50T         XCF128X           XC5VLX110T         XCF128X           XC5VLX110T         XCF128X           XC5VLX330T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X | FPGA           | Configuration Flash |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|

| XC5VLX50         XCF128X           XC5VLX85         XCF128X           XC5VLX110         XCF128X           XC5VLX155         XCF128X           XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX30T         XCF128X           XC5VLX30T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX50T         XCF128X           XC5VSX95T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX30T         XCF128X           XC5VFX100T         XCF128X           XC5VFX100T         XCF128X                                                                                                                                                                                                                                               | Virtex-5 FPGAs |                     |

| XC5VLX85         XCF128X           XC5VLX110         XCF128X           XC5VLX155         XCF128X           XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX330T         XCF128X           XC5VLX330T         XCF128X           XC5VSX55T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX30T         XCF128X           XC5VFX100T         XCF128X           XC5VFX100T         XCF128X                                                                                                                                                                                                                                                                                 | XC5VLX30       | XCF128X             |

| XC5VLX110         XCF128X           XC5VLX155         XCF128X           XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX20T         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX330T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX30T         XCF128X           XC5VFX100T         XCF128X           XC5VFX100T         XCF128X                                                                                                                                                                                                                                                                                | XC5VLX50       | XCF128X             |

| XC5VLX155         XCF128X           XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX20T         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                | XC5VLX85       | XCF128X             |

| XC5VLX220         XCF128X           XC5VLX330         XCF128X           XC5VLX20T         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX55T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX330T         XCF128X           XC5VLX330T         XCF128X           XC5VSX55T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                        | XC5VLX110      | XCF128X             |

| XC5VLX330         XCF128X           XC5VLX20T         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                        | XC5VLX155      | XCF128X             |

| XC5VLX20T         XCF128X           XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                           | XC5VLX220      | XCF128X             |

| XC5VLX30T         XCF128X           XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                               | XC5VLX330      | XCF128X             |

| XC5VLX50T         XCF128X           XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX50T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XC5VLX20T      | XCF128X             |

| XC5VLX85T         XCF128X           XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX50T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XC5VLX30T      | XCF128X             |

| XC5VLX110T         XCF128X           XC5VLX155T         XCF128X           XC5VLX220T         XCF128X           XC5VLX330T         XCF128X           XC5VSX35T         XCF128X           XC5VSX50T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XC5VLX50T      | XCF128X             |

| XC5VLX155T       XCF128X         XC5VLX220T       XCF128X         XC5VLX330T       XCF128X         XC5VSX35T       XCF128X         XC5VSX50T       XCF128X         XC5VSX95T       XCF128X         XC5VSX240T       XCF128X         XC5VTX150T       XCF128X         XC5VTX240T       XCF128X         XC5VFX30T       XCF128X         XC5VFX70T       XCF128X         XC5VFX100T       XCF128X         XC5VFX130T       XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XC5VLX85T      | XCF128X             |

| XC5VLX220T       XCF128X         XC5VLX330T       XCF128X         XC5VSX35T       XCF128X         XC5VSX50T       XCF128X         XC5VSX95T       XCF128X         XC5VSX240T       XCF128X         XC5VTX150T       XCF128X         XC5VTX240T       XCF128X         XC5VFX30T       XCF128X         XC5VFX70T       XCF128X         XC5VFX100T       XCF128X         XC5VFX130T       XCF128X         XC5VFX130T       XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XC5VLX110T     | XCF128X             |

| XC5VLX330T       XCF128X         XC5VSX35T       XCF128X         XC5VSX50T       XCF128X         XC5VSX95T       XCF128X         XC5VSX240T       XCF128X         XC5VTX150T       XCF128X         XC5VTX240T       XCF128X         XC5VFX30T       XCF128X         XC5VFX70T       XCF128X         XC5VFX100T       XCF128X         XC5VFX130T       XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XC5VLX155T     | XCF128X             |

| XC5VSX35T       XCF128X         XC5VSX50T       XCF128X         XC5VSX95T       XCF128X         XC5VSX240T       XCF128X         XC5VTX150T       XCF128X         XC5VTX240T       XCF128X         XC5VFX30T       XCF128X         XC5VFX70T       XCF128X         XC5VFX100T       XCF128X         XC5VFX130T       XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XC5VLX220T     | XCF128X             |

| XC5VSX50T         XCF128X           XC5VSX95T         XCF128X           XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XC5VLX330T     | XCF128X             |

| XC5VSX95T       XCF128X         XC5VSX240T       XCF128X         XC5VTX150T       XCF128X         XC5VTX240T       XCF128X         XC5VFX30T       XCF128X         XC5VFX70T       XCF128X         XC5VFX100T       XCF128X         XC5VFX130T       XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XC5VSX35T      | XCF128X             |

| XC5VSX240T         XCF128X           XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XC5VSX50T      | XCF128X             |

| XC5VTX150T         XCF128X           XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XC5VSX95T      | XCF128X             |

| XC5VTX240T         XCF128X           XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XC5VSX240T     | XCF128X             |

| XC5VFX30T         XCF128X           XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | XC5VTX150T     | XCF128X             |

| XC5VFX70T         XCF128X           XC5VFX100T         XCF128X           XC5VFX130T         XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XC5VTX240T     | XCF128X             |

| XC5VFX100T XCF128X<br>XC5VFX130T XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XC5VFX30T      | XCF128X             |

| XC5VFX130T XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XC5VFX70T      | XCF128X             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XC5VFX100T     | XCF128X             |

| XC5VFX200T XCF128X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XC5VFX130T     | XCF128X             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XC5VFX200T     | XCF128X             |

## **Family Description**

To achieve high-performance configuration, Platform Flash XL supports the SelectMAP configuration port with power-on synchronization and an immediate bitstream burst capability. A wide, 16-bit data bus delivers the bitstream synchronous to the FPGA configuration clock (CCLK) at up to 50 MHz in the Slave SelectMAP configuration mode without wait states. The device provides a READY\_WAIT signal that synchronizes the start of the FPGA configuration process, both improving system reliability and simplifying

board design. When the device signals a ready status after power-on, the device can immediately burst the FPGA design bitstream (.bit) file to the FPGA. The configuration performance of Platform Flash XL is ideal for PCI Express end-points and other high-performance applications (see Chapter 2, "High-Speed Configuration"). Platform Flash XL is optimized for the FPGA Slave SelectMAP configuration mode, but it also supports Master SelectMAP and Master BPI-Up modes (see Chapter 3, "Alternate Configuration Modes"). When the highest-performance configuration is required, the Platform Flash XL must be used with the FPGA in Slave SelectMAP mode. The Master SelectMAP or Master BPI can be considered in cases where less configuration performance is needed and the FPGA Fallback feature is needed.

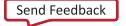

In addition to high-performance configuration, Platform Flash XL provides a 128 Mb (8M x 16 bits) nonvolatile single-chip flash memory configuration solution with a small footprint (FT64) and advanced system-level capabilities. A standard NOR flash interface (Figure 1-1) and support for common flash interface (CFI) queries provide industry-standard access to the device memory space. Platform Flash XL's 128 Mb capacity can hold one or more FPGA bitstreams, with any unused memory available for general-purpose data or embedded processor code storage. For bitstream requirements, see <u>UG191</u>, *Virtex-5 FPGA Configuration User Guide* or <u>UG360</u>, *Virtex-6 FPGA Configuration User Guide*.

Figure 1-1: Platform Flash XL Logic Diagram

The Platform Flash XL signals and functions are described in Table 1-2. See Chapter 2, "High-Speed Configuration" and Chapter 3, "Alternate Configuration Modes" for recommended connections to the FPGA.

Table 1-2: Platform Flash XL Signal Descriptions

| Signal Name | Function                           | Direction |

|-------------|------------------------------------|-----------|

| A[22:0]     | Address inputs                     | Inputs    |

| DQ[15:0]    | Data input/outputs, command inputs | I/O       |

| Ē           | Chip enable                        | Input     |

Table 1-2: Platform Flash XL Signal Descriptions (Cont'd)

| Signal Name             | Function                                           | Direction |

|-------------------------|----------------------------------------------------|-----------|

| G                       | Output enable                                      | Input     |

| $\overline{\mathbb{W}}$ | Write enable                                       | Input     |

| RP                      | Reset                                              | Input     |

| WP                      | Write protect                                      | Input     |

| K                       | Clock                                              | Input     |

| Ī                       | Latch enable                                       | Input     |

| READY_WAIT              | Ready wait                                         | I/O       |

| $V_{DD}$                | Supply voltage                                     | -         |

| $V_{\mathrm{DDQ}}$      | Supply voltage for input/output buffers            | -         |

| V <sub>PP</sub>         | Optional supply voltage for fast program and erase | _         |

| $V_{SS}$                | Ground                                             | _         |

| V <sub>SSQ</sub>        | Ground input/output supply                         | _         |

For FPGA designs that require data storage, the Platform Flash XL has a multiple-bank architecture—an array of 131 individually erasable blocks that are divided into sixteen 8 Mb banks. Fifteen main banks contain uniform blocks of 64 Kwords, and one parameter bank contains seven main blocks of 64 Kwords, plus four parameter blocks of 16 Kwords (the parameter blocks are located at the top of the memory address space in Platform Flash XL). The device has a 23-bit address bus providing random read access to each 16-bit word. See DS617, Platform Flash XL High-Density Configuration and Storage Device for memory map information and application programming instructions.

The device is in-system programmable with a 1.8V core (V<sub>DD</sub>) power supply (electronically erasable at the block level and programmable on a word-by-word basis). A separate I/O (V<sub>DDO</sub>) power supply enables I/O operation at 2.5V or 3.3V.

The ISE® iMPACT software supports indirect, in-system programming of Platform Flash XL via the IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE Std 1149.1) port (i.e., the JTAG port) on the FPGA (see Chapter 6, "Programming Platform Flash XL").

For FPGA configuration, the Platform Flash XL powers-on directly into synchronous read mode. After latching a starting read address, the synchronous read mode enables the flash to output its array data as a continuous stream of 16-bit words based on an internally incrementing address counter. In each clock cycle, a 16-bit word is delivered. The Platform Flash XL's interface can latch the starting address at the beginning of the FPGA's SelectMAP or BPI mode configuration sequence. The Platform Flash XL's synchronous read function is directly compatible with the FPGA's SelectMAP or BPI mode configuration interface.

# High-Speed Configuration

## Slave SelectMAP Configuration Mode

Applications including PCI Express<sup>®</sup> systems require fast FPGA configuration. Platform Flash XL provides the highest performance and power sequencing immunity in the Slave SelectMAP mode. Platform Flash XL achieves maximum configuration performance when a precise external clock source drives the FPGA Slave SelectMAP configuration mode up to the maximum 50 MHz burst read frequency limit (CCLK) of the device.

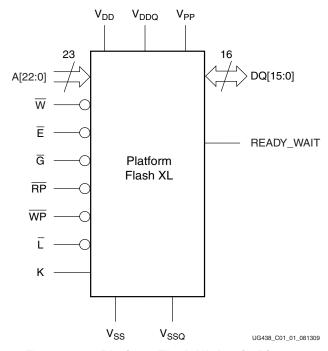

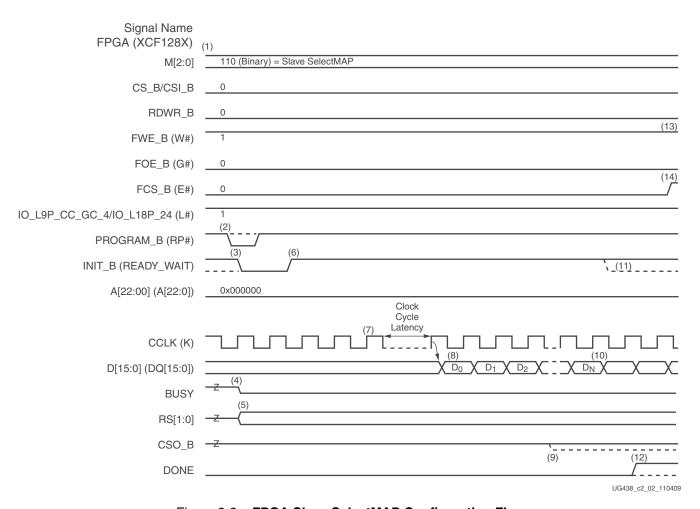

This chapter describes the configuration of an FPGA from Platform Flash XL in Slave SelectMAP configuration mode (M[2:0] = 110). The first section of this chapter describes the required setup for Slave SelectMAP configuration and indirect in-system Platform Flash XL programming (see Figure 2-1 and Figure 2-2). Next, the FPGA configuration flow for this mode is demonstrated (see Figure 2-3). Refer to the SelectMAP Configuration Interface section in <u>UG191</u>, *Virtex-5 FPGA Configuration User Guide* or <u>UG360</u>, *Virtex-6 FPGA Configuration User Guide*, for additional information on the Slave SelectMAP mode.

The Platform Flash XL has these system-level requirements for configuring an FPGA in the FPGA's SelectMAP mode:

- An external clock source drives the synchronous bitstream transfer resulting in a precise FPGA configuration time.

- On board pull-up or pull-down resistors set the configuration device control pins for output read mode.

- On board pull-up or pull-down resistors set the configuration device burst read start address.

- The FPGA does not support the Fallback feature in the Slave SelectMAP mode.

However, an external configuration manager (for example XAPP693, A CPLD-Based Configuration and Revision Manager for Xilinx Platform Flash PROMs and FPGAs) can be implemented to achieve the equivalent fallback function.

See Figure 2-1, page 16 or Figure 2-2, page 18 for example Slave SelectMAP configuration mode connections with the Virtex-5 FPGA or Virtex-6 FPGA, respectively. Refer to "Slave SelectMAP Configuration from Platform Flash XL," page 27 for details on the Slave SelectMAP configuration sequence.

Figure 2-1: Virtex-5 FPGA Slave SelectMAP Configuration Mode from Platform Flash XL

Notes relating to Figure 2-1:

- 1. The JTAG connections are shown for a simple, single-device JTAG scan chain. When multiple devices are on the JTAG scan chain, use the proper IEEE Std 1149.1 daisy-chain technique to connect the JTAG signals. The TCK signal integrity is critical for JTAG operation. Route, terminate, and if necessary, buffer the TCK signal appropriately to ensure signal integrity for the devices in the JTAG scan chain.

- 2. The FPGA mode (M[2:0]) pins are shown set to Slave SelectMAP mode (110). The implementation of a board-level option that enables the user to change the FPGA mode pins to JTAG mode (101) is recommended to enable JTAG-based debug capability for the FPGA during design prototyping without interference from the Slave SelectMAP configuration activities.

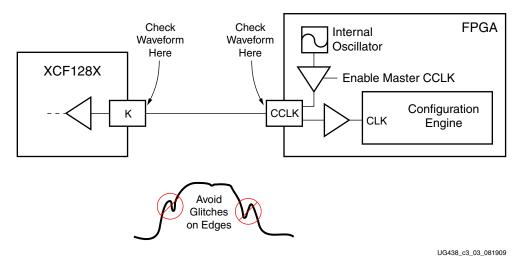

- 3. CCLK signal integrity is critical. Route and terminate the CCLK signal appropriately to ensure good signal integrity at the XCF128X  $\overline{K}$  pin and at the FPGA CCLK pin.

- 4. The iMPACT software requires the Virtex-5 FPGA's IO\_L9P\_CC\_GC\_4 connection to the device's L pin to support JTAG-based indirect programming.

- 5. The FPGA HSWAPEN pin is tied to ground in this sample schematic. HSWAPEN can alternatively be tied High. Review the FPGA configuration user guide for the effect of the alternate HSWAPEN setting.

- The Virtex-5 FPGA does not support AES decryption in the 16-bit-wide configuration mode shown in this sample schematic. Thus, the V<sub>BATT</sub> decryptor key battery power supply is unused and is tied to GND.

- The FPGA RS[1:0] pins are not connected in this basic configuration schematic. See <u>XAPP1100</u>, MultiBoot with Virtex-5 FPGAs and Platform Flash XL, for an example XCF128X implementation with MultiBoot support. Fallback is not supported in Slave SelectMAP mode.

- 8. DONE LED lights when DONE is High. INIT\_B/CRC-Error LED lights when INIT\_B is Low. Adjust the LED circuits and pull-up values for desired lighting results.

- 9. Each Platform Flash XL address pin requires a separate pull-down resistor to GND to ensure the XCF128X flash latches the zero address at the start of configuration.

- 10.  $V_{DDQ}$ ,  $V_{CCO}$  supplies, pull-up resistors, and  $V_{REF}$ , can alternately be connected to a 2.5V supply for I/O operation at 2.5V.

- 11. The required READY\_WAIT (INIT\_B) pull-up value is board dependent, but it must be strong enough to meet the READY\_WAIT rise time ( $T_{RWRT}$ ) requirement.

- 12. For the maximum clock frequency, see "Determining the Maximum Configuration Clock Frequency," page 45.

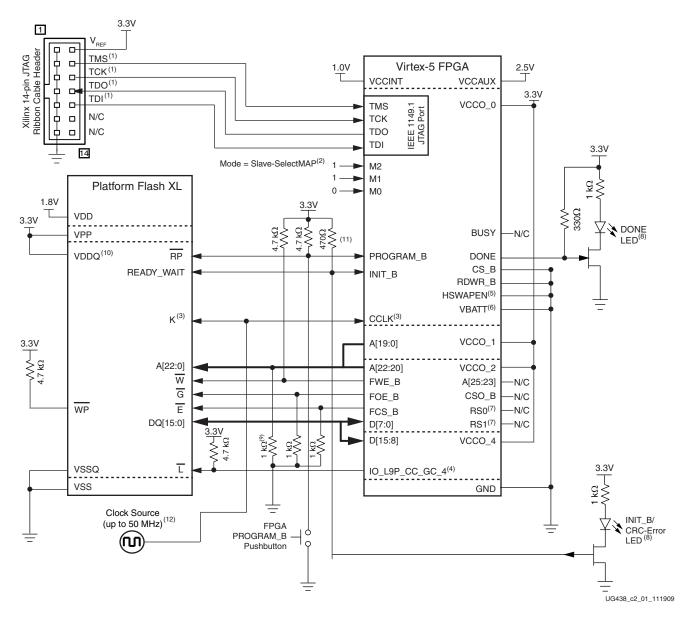

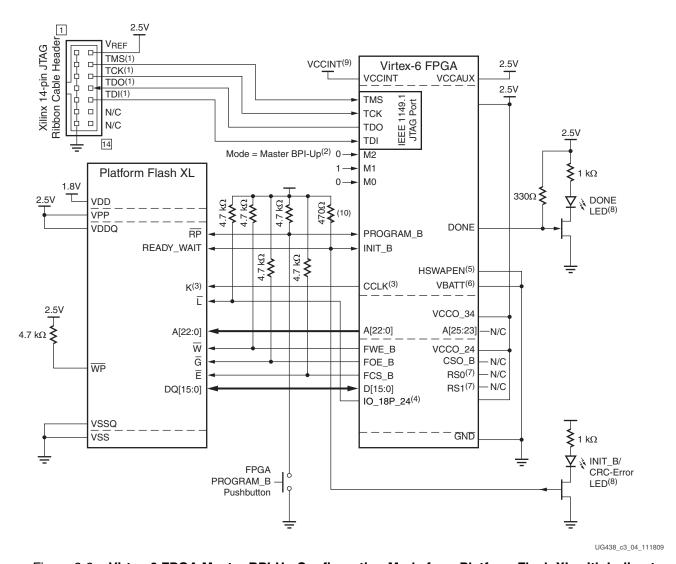

Figure 2-2 shows a Virtex-6 FPGA connected to Platform Flash XL for Slave SelectMAP configuration mode with indirect programming support.

Figure 2-2: Virtex-6 FPGA Slave SelectMAP Configuration Mode from Platform Flash XL

Notes relating to Figure 2-2:

- 1. The JTAG connections are shown for a simple, single-device JTAG scan chain. When multiple devices are on the JTAG scan chain, use the proper IEEE Std 1149.1 daisy-chain technique to connect the JTAG signals. The TCK signal integrity is critical for JTAG operation. Route, terminate, and if necessary, buffer the TCK signal appropriately to ensure signal integrity for the devices in the JTAG scan chain.

- 2. The FPGA mode (M[2:0]) pins are shown set to Slave SelectMAP mode (110). The implementation of a board-level option that enables the user to change the FPGA mode pins to JTAG mode (101) is recommended to enable JTAG-based debug capability for the FPGA during design prototyping without interference from the Slave SelectMAP configuration activities.

- 3. CCLK signal integrity is critical. Route and terminate the CCLK signal appropriately to ensure good signal integrity at the XCF128X K pin and at the FPGA CCLK pin.

- 4. The iMPACT software requires the Virtex-6 FPGA's IO\_L18P\_24 connection to the device's L pin to support JTAG-based indirect programming.

- The FPGA HSWAPEN pin is tied to ground in this sample schematic. HSWAPEN can alternatively be tied High. Review the FPGA data sheet for the effect of the alternate HSWAPEN setting.

- 6. The Virtex-6 FPGA does not support AES decryption in the 16-bit-wide configuration mode shown in this sample schematic. Thus, the  $V_{BATT}$  decryptor key battery power supply is unused and is tied to GND.

- 7. The FPGA RS[1:0] pins are not connected in this basic configuration schematic. See XAPP1100, MultiBoot with Virtex-5 FPGAs and Platform Flash XL, for an example XCF128X implementation with MultiBoot support. Fallback is not supported in Slave SelectMAP mode.

- 8. DONE LED lights when DONE is High. INIT\_B/CRC-Error LED lights when INIT\_B is Low. Adjust the LED circuits and pull-up values for desired lighting results.

- 9. Each Platform Flash XL address pin requires a separate pull-down resistor to GND to ensure the XCF128X flash latches the zero address at the start of configuration.

- 10. See <u>DS152</u>, Virtex-6 FPGA Data Sheet, for the V<sub>CCINT</sub> supply voltage.

- 11. The required READY\_WAIT (INIT\_B) pull-up value is board dependent, but it must be strong enough to meet the READY\_WAIT rise time ( $T_{RWRT}$ ) requirement.

- 12. For the maximum clock frequency, see "Determining the Maximum Configuration Clock Frequency," page 45.

The Slave SelectMAP configuration mode interface signals that influence the successful start and stop of data transfer are listed in Table 2-1.

Table 2-1: Platform Flash XL and FPGA SelectMAP Configuration Signals and Connections

| Platform<br>Flash XL<br>Pin Name | FPGA<br>Pin Name | Signal/Connection<br>Description                                                                                                                      | Function during FPGA Configuration                                                                                         | Function after<br>FPGA<br>Configuration | Function during<br>Indirect XCF128X<br>Programming                                                                                                                                                                                      |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N/A                              | TMS              | JTAG test mode select.<br>Connect from cable<br>header to TMS pin in all<br>devices in the JTAG<br>chain. Buffer as<br>necessary.                     | JTAG functionality is<br>always available. Do not<br>perform JTAG<br>operations during<br>SelectMAP<br>configuration. JTAG | JTAG functionality is always available. | JTAG is the required<br>access path to the<br>FPGA for indirect<br>programming of the<br>XCF128X. An FPGA<br>design (i.e., indirect                                                                                                     |

| N/A                              | TCK              | JTAG test clock. Connect<br>from cable header to TCK<br>pin in all devices in JTAG<br>chain. Signal integrity is<br>critical. Buffer as<br>necessary. | operations during configuration can interrupt the configuration sequence.                                                  |                                         | programming core) is downloaded through JTAG to the FPGA. This bridges the FPGA's JTAG port with the FPGA's pin interface to the XCF128X. Commands and data are sent and received through JTAG to the FPGA indirect programming core to |