Everything You Need to Know About DDR3

In the rapidly evolving world of memory technology, DDR3 SDRAM has emerged as a groundbreaking advancement, addressing the increasing demands for efficiency, performance, and scalability in modern computing. From innovative features like Command Write Delay (CWD) and On Die Calibration Engine (ODCE) to notable enhancements in power management and thermal control, DDR3 introduces a host of capabilities that redefine memory performance. This article explores the key features, architectural improvements, and practical applications of DDR3, shedding light on how it surpasses its predecessor, DDR2, and sets a new standard in memory design for both consumer and industrial applications.Catalog

Overview

CWD, or Command Write Delay, is a mechanism designed to optimize write delays in memory systems, enhancing data management efficiency. The Reset command activates a super power-saving mode in DDR3 SDRAM, halting memory operations and shifting the system into low-energy standby. This feature conserves energy and extends memory lifespan, making it mostly valuable for mobile and embedded applications where power efficiency is used.

The ZQ function advances terminal resistance calibration through the On Die Calibration Engine (ODCE), fine-tuning On Die Termination (ODT) resistance to maintain signal integrity under varying conditions. This calibration mitigates risks like signal degradation that can compromise data accuracy and system stability. High-performance computing environments highlight the reliability improvements these optimizations provide, especially in applications demanding consistent performance.

The Self-Reflash Temperature (SRT) function integrates programmable temperature control for present adjustments to memory clock speeds based on thermal conditions. This enhances power management and prevents overheating, a common challenge that can lead to throttling or component failure. Additionally, the Partial Array Self-Refresh (PASR) feature selectively refreshes active memory segments, significantly reducing power consumption. This targeted approach to resource management is widely recognized as an effective strategy for optimizing memory performance without sacrificing efficiency, mostly in systems with irregular memory usage patterns.

New Design of DDR3

The DDR3 memory architecture introduces an innovative 8-bit prefetch design, which effectively doubles the previous 4-bit prefetch characteristic found in DDR2. This advancement allows the DRAM core to function at just 1/8 of the data frequency. For instance, DDR3-800 operates at a core frequency of merely 100MHz, showcasing a significant leap in efficiency.

Key features of this design include:

• The implementation of a point-to-point topology, which significantly reduces the load on address, command, and control buses, leading to enhanced overall system performance.

• A manufacturing process that falls below 100nm, resulting in a decrease in operating voltage from 1.8V in DDR2 to 1.5V. This reduction not only fosters energy efficiency but also promotes better thermal management within the system.

• The introduction of asynchronous reset and ZQ calibration functionalities, marking a meaningful transformation in design that boosts operational stability and efficiency.

These enhancements reflect a thoughtful approach to memory architecture, aiming to meet the evolving demands of modern computing while considering aspects like energy consumption and system performance.

DDR2 and DDR3 Comparison

|

Feature |

DDR2 |

DDR3 |

|

Burst Length (BL) |

BL=4 is commonly used |

BL=8 is fixed; supports a 4-bit Burst Chop (BL=4 read +

BL=4 write to synthesize BL=8). Controlled via A12 address line. Burst

interrupt is prohibited |

|

Addressing Timing |

CL range: 2–5; Additional Latency (AL) range: 0–4 |

CL range: 5–11; AL options: 0, CL-1, CL-2. Adds Write

Delay (CWD) based on operating frequency |

|

Reset Function |

Not available |

Newly introduced. A dedicated reset pin simplifies

initialization, reduces power consumption, and halts internal functions

during reset |

|

ZQ Calibration |

Not available |

Introduced with a ZQ pin using a 240-ohm reference

resistor. Automatically calibrates data output and ODT resistance |

|

Reference Voltage |

Single reference voltage (VREF) |

Divided into two signals: VREFCA (command/address) and

VREFDQ (data bus), improving signal-to-noise ratio |

|

Point-to-Point Connection (P2P) |

Multiple memory channels supported per controller |

Memory controller handles one channel with one slot,

enabling P2P or P22P relationships. Reduces bus load and improves

performance |

|

Power Consumption |

Standard self-refresh mechanisms |

Advanced features like automatic self-refresh and partial

self-refresh based on temperature, leading to better efficiency |

|

Applications |

Primarily used in desktops and servers |

Ideal for mobile devices, servers, and desktops due to

high frequency, speed, and lower power consumption |

|

Future Platform Support |

Supported on legacy systems and current platforms |

Supported by Intel's Bear Lake and AMD K9 platforms for

future compatibility |

Memory Improvements of DDR3

Logical Banks

The evolution from DDR2 to DDR3 represents a notable shift in-memory architecture, initiating with 8 logical banks and the potential to expand up to 16. This development goes beyond technical enhancements; it mirrors an increasing demand for high-capacity chips capable of handling complex applications. As both software and hardware requirements continue to rise, the ability to support more logical banks becomes increasingly relevant. Experiences across various industries suggest that systems designed with scalability in mind often provide greater long-term returns, as they can adjust to future technical changes without the need for extensive overhauls.

Packaging

The DDR3 packaging signifies a remarkable advancement in engineering, highlighted by a higher pin count that enables new functionalities. The transition from DDR2's 60/68/84-ball FBGA packages to the 78-ball FBGA for 8-bit chips and the 96-ball FBGA for 16-bit chips illustrates this leap. This improvement not only enhances data transfer capabilities but also reflects a growing commitment to sustainability, as DDR3 complies with strict environmental standards, eliminating harmful substances. In today’s manufacturing landscape, you can be increasingly drawn to products that prioritize ecological responsibility, emphasizing the need to weave sustainable practices into high-tech innovations.

Power Consumption

A standout feature of DDR3 is its capacity to deliver high bandwidth while significantly minimizing power consumption. By reducing the operating voltage from DDR2's 1.8V to 1.5V, DDR3 is projected to use 30% less power overall. The power ratios for DDR3-800, 1066, and 1333—0.72X, 0.83X, and 0.95X respectively—demonstrate a clear path toward enhanced performance and efficiency. This decrease in power consumption not only supports environmental sustainability but also prolongs the device's lifespan, as reduced heat generation leads to less thermal stress on components. Historical data from various sectors indicate that energy-efficient technologies tend to lower operational costs over time, reinforcing the value of DDR3.

Pros in Performance

|

Performance Advantage |

Details |

|

Less Power Consumption and Heat |

DDR3 draws lessons from DDR2, reducing energy consumption

and heat while maintaining cost control. This makes DDR3 more appealing to you |

|

Higher Operating Frequency |

Due to lower energy consumption, DDR3 achieves higher

operating frequencies, compensating for longer delay times and serving as a

selling point for graphics cards |

|

Reduced Graphics Card Cost |

DDR3 uses larger memory particles (32M x 32-bit),

requiring fewer chips to achieve the same capacity as DDR2, reducing PCB

area, power consumption, and cost |

|

Improved Versatility |

DDR3 offers better compatibility with DDR2 due to

unchanged key features (pins, packaging), enabling easier integration with

existing DDR2 designs |

|

Wide Adoption |

DDR3 is widely used in new high-end graphics cards and

increasingly adopted in low-end graphics cards |

Growth History

The DDR3 memory standard, officially unveiled by JEDEC on June 28, 2002, represented a major moment in the evolution of memory technology. Yet, it wasn't until 2006 that DDR2 truly began to carve out its niche in the marketplace. This lag in widespread acceptance did not deter manufacturers from eagerly pursuing DDR3 solutions, highlighting a visionary approach to memory technology that would ultimately transform the industry.

Market Share

Market analysts, including those from iSuppli, anticipated that by 2008, DDR3 would establish a dominant position within the memory sector, forecasting a market share of 55%. By the close of 2008, DDR3 memory modules, operating at frequencies of 1066, 1333, and 1600 MHz, became readily available to consumers. While DDR3 shared architectural similarities with DDR2, it effectively tackled the shortcomings of its predecessor, facilitating a smoother transition and fostering broader acceptance. This progression illustrates the value of flexibility in technical advancements, as you can adeptly respond to consumer needs while simultaneously enhancing performance metrics.

New Features

DDR3 memory brings substantial enhancements over DDR2, featuring elevated data transfer rates, an innovative topology for address and control buses, and improved energy efficiency. The introduction of an 8-bit prefetch design combined with a point-to-point architecture not only optimizes operations but also elevates overall performance. These improvements mirror a wider trend in technology where speed and efficiency reign supreme. Insights from various sectors reveal that those who embrace innovation often secure a competitive edge, evidenced by the swift adoption of DDR3 across multiple applications.

Capacity Milestone

In late 2009, Samsung captured attention with the release of a groundbreaking 4Gb DDR3 chip fabricated using a 50nm process, enabling the creation of 32GB memory sticks and significantly enhancing the potential of 64-bit computing. This chip also boasted an impressive 40% reduction in power consumption compared to earlier generations. Projections indicating a rise in DDR3's market share to 72% by 2011 further accentuated the natural progression from DDR2 to DDR3. This shift serves as a reminder of the cyclical nature of technological advancement, where each new iteration builds upon its predecessor, driving innovation and efficiency in an ever-changing digital environment.

About us

ALLELCO LIMITED

Read more

Quick inquiry

Please send an inquiry, we will respond immediately.

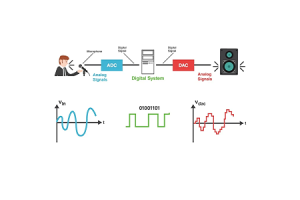

Digital Signal Processing: Principles and Applications

on December 30th

Exploring Block RAM in Xilinx SP3 Series: Features, Differences, and Optimization

on December 30th

Popular Posts

-

Complex Instruction Set Computers: How They Changed Computing?

on April 18th 147749

-

USB-C Pinout and Features

on April 18th 111920

-

Using Xilinx Unified Simulation Primitives: A Comprehensive Guide to FPGA Design and Simulation

on April 18th 111349

-

Power Supply Voltages in Electronics: Meaning of VCC, VDD, VEE, VSS, and GND

on April 18th 83714

-

RJ45 Connector Guide: Pinout, Wiring, Cable Types, and Uses

on January 1th 79502

-

The Ultimate Guide to Wire Color Codes in Modern Electrical Systems

The way our electrical systems use colors isn’t just for looks. Each wire color now indicates a specific function, making it easier to identify and handle electrical components correctly during ins...on January 1th 66872

-

Quality (Q) Factor: Equations and Applications

The quality factor, or 'Q', is important when checking how well inductors and resonators work in electronic systems that use radio frequencies (RF). 'Q' measures how well a circuit minimizes energy...on January 1th 63005

-

Purge Valve Guide: Function, Symptoms, Testing, and Replacement for Optimal Engine Performance

The purge valve is a key part of a car’s system that helps keep the air clean by managing fuel vapors before they can escape into the atmosphere. This not only helps the environment by reducing pol...on January 1th 62952

-

Achieving Peak Performance with the Maximum Power Transfer Theorem

The Maximum Power Transfer Theorem explains how energy from a source, such as a battery or generator, flows to a connected load. It shows the exact condition where the load receives the most power....on January 1th 54078

-

A23 Battery Specifications and Compatibility

The A23 battery is a small, cylinder-shaped battery with high voltage. Also called 23A, 23AE, or MN21, it runs at 12 volts and much higher than AA or AAA batteries. Its special design make...on January 1th 52092